Д. Онышко

Синтезатор частоты UMA1021M фирмы Philips Semiconductors

Фирма Philips Semiconductors является одним из основных производителей дешёвых синтезаторов частоты, которые широко распространяются в России. На базе этих синтезаторов строятся модули радиоканалов для автомобильной сигнализации, систем сбора и обработки информации с удалённых объектов и датчиков, систем безопасности и контроля доступа, а также систем радиотелефонии. В данной статье речь пойдёт об одном из синтезаторов семейства UMA. Все микросхемы данного семейства имеют одну и ту же функциональную структуру и отличаются, как правило, лишь техническими характеристиками.

Микросхема UMA1021M имеет в своём составе все элементы, необходимые для построения синтезатора частоты с ФАПЧ, за исключением ГУН (генератора управляемого напряжением), генератора образцовой частоты и ФНЧ.

Особенности микросхемы UMA1021M:

- малое энергопотребление/режим powerdown;

- маленький корпус SSOP-20;

- очень малые шумы (-90 дБм/Гц);

- быстрый последовательный интерфейс (скорость обмена 10 МГц);

- полностью программируемые делители частоты;

- программируемое двухуровневое устройство накачки заряда (charge pump, согласно определению фирмы Philips);

- детектор выхода из фазового синхронизма.

Микросхема разработана для использования в системах радиотелефонии с питанием от трёх NiCd батареек, с низким током потребления и номинальным напряжением питания 3 В.

В состав UMA1021M входят: встроенный BiCMOS предделитель частоты, цифровой делитель входной частоты с программируемым коэффициентом деления (17 бит), делитель образцовой частоты (11 бит), цифровой фазовый детектор, двухуровневый Charge pump и устройство обмена информацией с внешним устройством (контроллером) по последовательному протоколу. Структурная схема и маркировка выводов прибора показана на рис. 1.

Рисунок 1. Структурная схема синтезатора

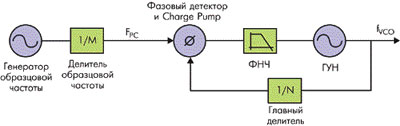

Структурная схема синтезатора с ФАПЧ изображена на рис. 2.

Рисунок 2. Синтезатор с ФАПЧ

Напряжения питания VDD1 и VDD2 должны иметь потенциал, равный VDD , причём для обеспечения большого диапазона управляющих напряжений для ГУН необходимо, чтобы VCC было больше VDD (например: VCC = 5 В, а VDD = 3 В).

Фазовый детектор

Фазовый детектор чувствителен как к фазе, так и к частоте, он реагирует на очень маленькие разности фаз сигналов с выходов главного и образцового делителей. Принцип работы фазового детектора изображён на рис. 3. Частота сравнения FPC фазового детектора типична для систем радиосвязи (табл. 1).

Рисунок 3. Работа фазового детектора

Таблица 1. Основные технические характеристики синтезатора

| Параметр | Обозначение | Мин. | >Тип. | Макс. |

| Напряжение питания цифровой части, В | VDD | 2,7 | 5,5 | |

| Напряжение питания аналоговой части, В | VCC | 2,7 | 5,5 | |

| Потребляемый ток, мА | IDD + ICC | 10 | ||

| Общий потребляемый ток в режиме power-down, мкА | IDD(PD) + ICC(PD) | 5 | 50 | |

| Входная частота, МГц | fRF | 300 | 200 | |

| Образцовая частота (частота кварцевого резонатора), МГц | fxtal | 3 | 35 | |

| Коэффициент деления главного делителя | N | 512 | 131071 | |

| Коэффициент деления делителя образцовой частоты | M | 8 | 2047 | |

| Максимальная частота сравнения, кГц | FPC | 2000 | ||

| Частота фазового компаратора, кГц | fPC | 200 | ||

| Уровень входного сигнала, мВ | VRF | 50 | 225 | |

| Допустимый температурный интервал, ºC | Tamb | -30 | +85 | |

| Рассеиваемая мощность, мВт | P | 150 |

Когда петля находится в режиме "захвата" (lock), то есть когда погрешность фазы на входе фазового детектора равна нулю, выход устройства charge pump находится в высокоимпедансном состоянии. Когда петля находится вне режима "захвата", то есть когда фазовым детектором замечена погрешность фазы между входными сигналами, устройство charge pump посылает импульсы исправления петлевому фильтру. Длительность импульсов пропорциональна погрешности фазы. В зависимости от того, какой из сигналов, поступающих на фазовый детектор, опережает другой, выход устройства charge pump переключается либо в режим поглощения, либо в режим источника тока, тем самым заряжая или разряжая конденсаторы в петлевом фильтре до напряжения, необходимого для перевода петли ФАПЧ в режим захвата. Величина тока устройства charge pump (ширина положительного и отрицательного импульсов на рис. 3) выбирается программно. Отношение токов двух устройств charge pump ICPF/ICP может варьироваться от 4 до 16 (табл. 2). Ток ICPF обеспечивает быструю настройку на заданную частоту, правда, менее точную, по сравнению с ICP. Величина этих токов зависит от тока ISET, который устанавливается аппаратно с помощью резистора, подключаемого к одноимённому выводу на землю. При значениях данного резистора от 5,6 до 12 кОм величина тока ISET находится в интервале от 200 до 100 мкА. Работа CPF может быть запрещена аппаратно путём подачи сигнала управления на вход FAST.

Таблица 2. Значение токов Charge pump

| Cr1 | Cr0 | ICP | ICPF | ICPF : ICP |

| 0 | 0 | 2 x ISET* | 8 x ISET | 4:1 |

| 0 | 1 | 2 x ISET | 16 x ISET | 8:1 |

| 1 | 0 | 1 x ISET | 12 x ISET | 12:1 |

| 1 | 1 | 1 x ISET | 16 x ISET | 16:1 |

*) ISET = VSET/RSET , где VSET - типовое значение регулирующего напряжения (VSET = 1,2 В).

Запись данных в синтезатор

Запись данных в синтезатор осуществляется по трёхпроводной шине (данные передаются по линии DATA, синхронизация - CLK и разрешение записи - E). После програмного или аппаратного выхода из режима powerdown нет необходимости в перепрограммировании синтезатора, так как предыдущие данные в нём будут сохранены. Вид управляющих сигналов представлен на рис. 4.

Рисунок 4. Протокол записи

Время положительного и отрицательного перепадов синхроимпульсов не должно превышать 40 нс. Первым вводится бит данных d16 (табл. 3), последним - адресный бит ad0 (для коэффициентов деления первым вводится N16 (M10)). Данные загружаются в адресный регистр по переходу сигнала разрешения E в высокое состояние. Действительными являются только последние 21 бит, остальные системой не учитываются.

Таблица 3. Формат данных

| Поле данных | Поле адреса | |||||||||||||||||||

| d16 | d15 | d14 | d13 | d12 | d11 | d10 | d9 | d8 | d7 | d6 | d5 | d4 | d3 | d2 | d1 | d0 | ad3 | ad2 | ad1 | ad0 |

| X* | X | X | X | Ool | X | Cr1 | Cr0 | X | X | tpol | X | X | X | X | X | X | 0 | 0 | 0 | 1 |

| N16 | Коэффициент деления главного делителя | N0 | 0 | 1 | 0 | 0 | ||||||||||||||

| X | X | X | X | X | X | M10 | Коэф. деления делителя обр. частоты | M0 | 0 | 1 | 0 | 1 | ||||||||

*)X - не используется.

Детектор захвата петли ФАПЧ

В течение переходного процесса при установке новой частоты или когда фазовая ошибка больше чем 20 нс, на контрольном выводе LOCK фазовый детектор формирует сигнал лог. 0, в противном случае - лог. 1 ( рис. 5).

Рисунок 5. Работа детектора захвата петли

Данный вывод микросхемы удобно использовать для бесшумной перестройки радиотракта. Запретить (или разрешить) работу детектора захвата петли ФАПЧ можно программно, записав в разряд Ool - 0 (1). Когда работа детектора запрещена, на выводе LOCK на время запрета присутствует лог. 1. На выходе детектора включен транзистор с открытым стоком, поэтому рекомендуется к выводу LOCK подключить резистор на шину питания.

Режим Powerdown

Синтезатор находится в рабочем режиме, когда на выводе PON и в разряде tpol присутствует "активный уровень", иначе синтезатор переходит в режим powerdown. Активный уровень задаётся логическим уровнем на выводе POL. Микросхема UMA1021M имеет очень низкий потребляемый ток в режиме powerdown, составляющий не более 50 мкА.

Заключение

Фирма Philips специально для удобства пользователя разработала программное обеспечение, с помощью которого он может рассчитать ФНЧ третьего и четвёртого порядка, а также производить отладку аппаратной части своей системы на основе синтезатора, путём подключения её к LPT-порту персонального компьютера. Помимо этого, разработаны так называемые Evaluation board (оценочные платы) на основе различных синтезаторов, которые также подключаются к LPT-порту. На основе данных оценочных плат можно легко построить цифровые беспроводные системы, такие как DCS1800, PHS и так далее.

|

Автор документа: Сергей Гаврилюк

, http://www.gaw.ru" |

Дата публикации: 07.08.2007 Дата редактирования: 05.01.2008 |

| Кол-во просмотров 4804 | |