# STR91xF Errata sheet

### Rev B and D limitations and corrections

### Silicon identification

STR9 microcontrollers have two major salestype groups, as follows:

- The initial group consists of devices STR91xFxxxxx, for example STR912FW44X6, with silicon revisions B, and D. Detailed technical information for these devices may be found in the STR91xF datasheet and STR91xF reference manual documents.

- The second group consists of devices STR91xFAxxxxx, for example STR912FAW44X6, with a later silicon revision. Detailed technical information for these devices may be found in the STR91xFA datasheet and STR91xFA reference manual documents.

This errata document covers the first group with rev B and rev D.

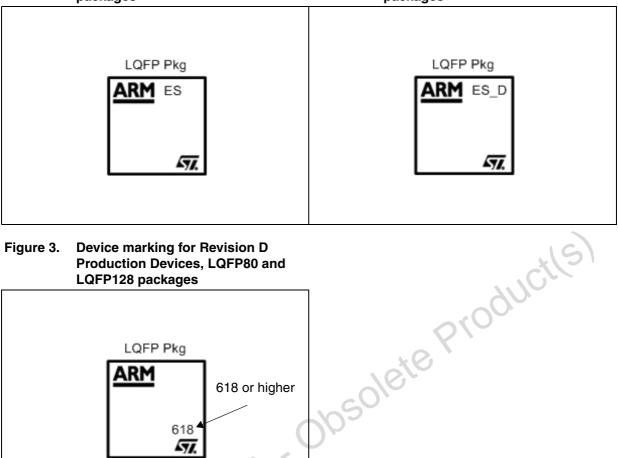

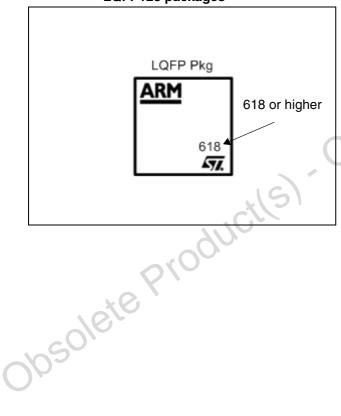

Table 1 summarizes the marking to assist identification. Figure 1 through Figure 3 represent where the physical marking may be found on the devices.

Table 1. Device identification

| Salestype<br>Group, External<br>marking | Internal<br>Silicon<br>Revision | External Marking | Note                                                                                                                     |  |  |

|-----------------------------------------|---------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| STR91xFxxxxx D                          | В                               | ES               | Ir that Engineering Samples. LQFP128 pkgs.                                                                               |  |  |

|                                         |                                 | ES D             | see Figure 2. Rev D Engineering Samples before week 18 of 2006. LQFP128 packages.                                        |  |  |

|                                         |                                 |                  | see Figure 3. Production Rev D Devices on or after week 18 of 2006. LQFP80 and LQFP128 packages. Date code format = YMM. |  |  |

| josolete P                              |                                 |                  |                                                                                                                          |  |  |

Figure 1. **Device marking for Revision B Engineering Samples, LQFP128** packages

Figure 2. **Device marking for Revision D Engineering Samples, LQFP128** packages

Figure 3. **Device marking for Revision D** Production Devices, LQFP80 and LQFP128 packages

577 2/22

STR91xF Contents

# **Contents**

| 1    | Produ  | uct evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 5 |

|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2    | Silico | on limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 7 |

|      | 2.1    | VIC interrupt controller wrong vector fetch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 7 |

|      | 2.2    | Motor control emergency pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 7 |

|      | 2.3    | USB CRC computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 8 |

|      | 2.4    | BSPI transmit DMA request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 8 |

|      | 2.5    | I2C BUSY bit not cleared by bus error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 8 |

|      | 2.6    | UART error handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 8 |

|      | 2.7    | PFQBC/LDMA load multiple (performance related)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 8 |

|      | 2.8    | RTC periodic interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 9 |

|      | 2.9    | PLL register default value for 48 MHz clock out of spec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 9 |

|      | 2.10   | Flash memory read configuration register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 9 |

|      | 2.11   | io. programming speed in the interest in the i |     |

|      | 2.12   | Flash memory device security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10  |

|      | 2.13   | Flash memory cannot be uploaded by JTAG tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10  |

|      | 2.14   | Clock control unit clock switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10  |

|      | 2.15   | SRAM discharge delay after tamper event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11  |

|      | 2.16   | Flash memory status register bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11  |

|      | 2.17   | Sleep mode / Idle Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11  |

|      | 2.18   | Flash memory sector protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12  |

|      | 2.19   | System reset at 96 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12  |

|      | 2.20   | Waking up from Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13  |

|      | 2.21   | Flash memory erase and programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13  |

| ~O)/ | 2.22   | Sleep Mode Current (I <sub>SLEEP</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14  |

| 102  | 2.23   | Exit from Sleep and Idle Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | 2.24   | Sleep and Idle Mode Timing Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14  |

|      | 2.25   | Wake Up Event Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15  |

|      | 2.26   | ETM (Embedded Trace Module) Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16  |

|      | 2.27   | Disabling the Watchdog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

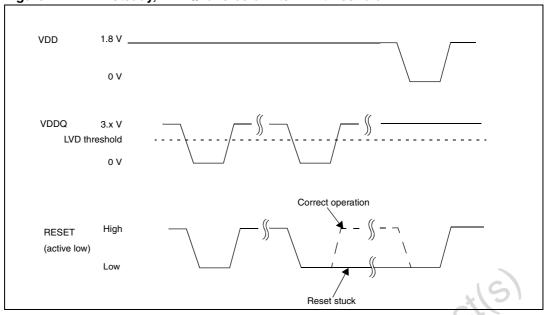

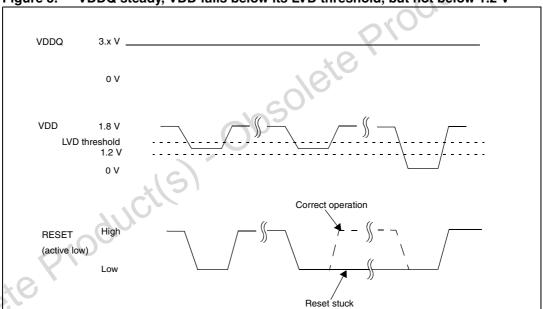

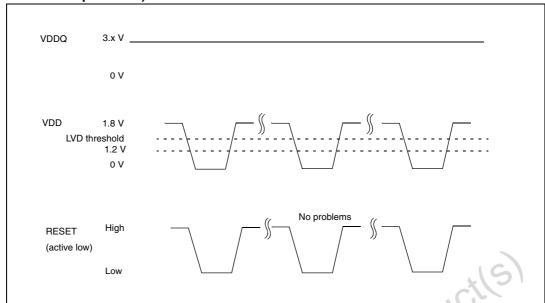

|      | 2.28   | LVD (Low Voltage Detect) and VDD fall time requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

**577**

| ••••• |  |  | 01110 |  |

|-------|--|--|-------|--|

|       |  |  |       |  |

|       |  |  |       |  |

|       |  |  |       |  |

|       |  |  |       |  |

| 3 | Revis | sion history                                              | 21 |

|---|-------|-----------------------------------------------------------|----|

|   | 2.33  | ADC input range                                           | 20 |

|   | 2.32  | 16-bit pre-scaled clock source for general purpose timers | 20 |

|   | 2.31  | Motor Control output polarity                             | 19 |

|   | 2.30  | ADC interrupt generation                                  | 19 |

|   | 2.29  | LVD Logic may hold reset active inappropriately           | 17 |

|   |       |                                                           |    |

Obsolete Productis). Obsolete Productis)

STR91xF

Contents

STR91xF Product evolution

# 1 Product evolution

This table summarizes the fix plan status for the next silicon revision ( $\bullet$  = fix). Table 2. Product evolution summary

| Section      | Limitation                                               | Fixed in Rev D                 | Fixed in<br>STR91xFA<br>Series |

|--------------|----------------------------------------------------------|--------------------------------|--------------------------------|

| Section 2.1  | VIC interrupt controller wrong vector fetch              | •                              | •                              |

| Section 2.2  | Motor control emergency pin                              | • 1 and 2;<br>workaround for 3 | •                              |

| Section 2.3  | USB CRC computation                                      | •                              | •                              |

| Section 2.4  | BSPI transmit DMA request                                | •                              | •                              |

| Section 2.5  | I2C BUSY bit not cleared by bus error                    | •                              | •                              |

| Section 2.6  | UART error handling                                      | •                              | •                              |

| Section 2.7  | PFQBC/LDMA load multiple (performance related)           | •                              | cils                           |

| Section 2.8  | RTC periodic interrupt                                   | workaround                     | workaround                     |

| Section 2.9  | PLL register default value for 48 MHz clock out of spec. | workaround                     | •                              |

| Section 2.10 | Flash memory read configuration register                 | 2. •                           | •                              |

| Section 2.11 | ISP programming speed                                    | •                              | •                              |

| Section 2.12 | Flash memory device security                             | •                              | •                              |

| Section 2.13 | Flash memory cannot be uploaded by JTAG tool             | •                              | •                              |

| Section 2.14 | Clock control unit clock switching                       | workaround                     | •                              |

| Section 2.15 | SRAM discharge delay after tamper event                  | •                              | •                              |

| Section 2.16 | Flash memory status register bit 7                       | workaround                     | workaround                     |

| Section 2.17 | Sleep mode / Idle Mode                                   | workaround                     | •                              |

| Section 2.18 | Flash memory sector protection                           | workaround                     | workaround                     |

| Section 2.19 | System reset at 96 MHz                                   | workaround                     | •                              |

| Section 2.20 | Waking up from Sleep Mode                                | workaround                     | workaround                     |

| Section 2.21 | Flash memory erase and programming                       | workaround                     | •                              |

| Section 2.22 | Sleep Mode Current (I <sub>SLEEP</sub> )                 | no solution                    | •                              |

| Section 2.23 | Exit from Sleep and Idle Mode                            | workaround                     | •                              |

| Section 2.24 | Sleep and Idle Mode Timing Requirements                  | workaround                     | workaround                     |

| Section 2.25 | Wake Up Event Configuration                              | workaround                     | workaround                     |

| Section 2.26 | ETM (Embedded Trace Module) Configuration                | workaround                     | workaround                     |

| Section 2.27 | Disabling the Watchdog                                   | no solution                    | •                              |

5/22

Product evolution STR91xF

Table 2. Product evolution summary

|        | Section      | Limitation                                                | Fixed in Rev D | Fixed in<br>STR91xFA<br>Series |

|--------|--------------|-----------------------------------------------------------|----------------|--------------------------------|

|        | Section 2.28 | LVD (Low Voltage Detect) and VDD fall time requirement    | workaround     | •                              |

|        | Section 2.29 | LVD Logic may hold reset active inappropriately           | workaround     | •                              |

|        | Section 2.30 | ADC interrupt generation                                  | workaround     | workaround                     |

|        | Section 2.31 | Motor Control output polarity                             | no solution    | •                              |

|        | Section 2.32 | 16-bit pre-scaled clock source for general purpose timers | no solution    | workaround                     |

|        | Section 2.33 | ADC input range                                           | no solution    | spec changed                   |

| Obsole | te Prod      | ADC input range                                           | s Prodi        |                                |

### 2 Silicon limitations

### 2.1 VIC interrupt controller wrong vector fetch

#### **Description of limitation in Rev B**

The CPU may read an incorrect interrupt vector if an asynchronous interrupt happens on VIC0 while there is a pending vectored interrupt on VIC1

**Fixed in Rev D.** Swapped asynchronous USB Resume interrupt input channel with synchronous CCU interrupt.

New channel assignment in rev D:

USB Resume Interrupt is moved to VIC1 channel 30 (was on VIC0, channel 10),

Clock Control Unit CCU Interrupt is moved to VIC0 channel 10 from VIC1 channel 30

### 2.2 Motor control emergency pin

#### **Description of limitation in Rev B**

- 1. Emergency Stop (EST) pin (P6.7) is always connected as an input. Emergency Stop can be activated even if the pin is configured for a different IO function.

- 2. The Emergency Stop input signal is active-high (a typical emergency stop input is active-low, open drain).

- 3. The PWM outputs can be resumed by writing 0x4321 in the MC\_ESC register and the motor will restart, even if the emergency pin is still active.

#### 1 and 2 fixed in Rev D.

Added bit 6 (EST Dis) to MC PCR1 register. When set, the bit blocks EST input from GPIO.

The EST input polarity is changed from active-high to active-low.

#### Workaround for 3 using Rev D

- Read EST pin until it is de-asserted

- Mask FIQ/IRQ to prevent the next two write operations to the MC\_ESC register from being interrupted

- Write 4321h to MC\_ESC register to restart the PWM

- Write 0000h to MC\_ESC register to re-arm the EST

- Unmask FIQ/RIQ

Item 3 is fixed in STR91xFA series devices.

### 2.3 USB CRC computation

#### Description of limitation in Rev B

When a packet is received with one specific wrong CRC (very rare), the packet is acknowledged whereas no acknowledgement should be sent.

This issue occurs when the CRC computation result is completed prematurely, just before the last bit of the packet, and the packet is accepted.

**Fixed in Rev D.** The CRC computation result is compared after the reception of the last bit, eliminating the possibility of a premature CRC calculation.

### 2.4 BSPI transmit DMA request

#### Description of limitation in Rev B

The DMA Requests signals are active at power-up and cleared only when the SPI block is enabled. This can cause spurious DMA requests if the BSPI DMA channels are configured before enabling the BSPI block.

Fixed in Rev D. The DMA Transmit Requests from BSPI are cleared (de-activated) at reset.

# 2.5 I2C BUSY bit not cleared by bus error

#### **Description of limitation in Rev B**

The BUSY bit is set by a Start condition and cleared by a Stop condition. But if a Bus Error occurs, the BUSY bit is cleared even if there is still activity on the bus.

Fixed in Rev D. The BUSY bit is not cleared inappropriately by a Bus Error.

## 2.6 UART error handling

#### Description of limitation in Rev B

When there are 2 consecutive frame errors or break errors, the error flags in the Status register are not set by the second one.

**Fixed in Rev D.** A second consecutive frame or break error will set the appropriate flags in UART status register.

# 2.7 PFQBC/LDMA load multiple (performance related)

#### **Description of limitation in Rev B**

When the LDMA instruction is executed, multiple CPU registers are loaded with data from the Flash program memory. This instruction fetches data from the Flash memory by issuing a Read bus cycle for each of the data words.

**Fixed in Rev D.** The LDMA instruction fetches the data from the Flash memory in burst mode, one clock per word instead of one bus cycle per word. This greatly reduces the instruction execution time.

### 2.8 RTC periodic interrupt

#### Description of limitation for all silicon revisions

When reading the Status register for the Periodic Interrupt flag, the CPU may occasionally miss the flag's set status.

#### Workaround

Do not poll the RTC interrupt flag. Always use the RTC interrupt signal to the VIC to cause a standard interrupt. This will not be fixed in future silicon revisions.

### 2.9 PLL register default value for 48 MHz clock out of spec.

#### Description of limitation in Rev B and Rev D

The default reset value of the SCU\_PLL Configuration register should result in a PLL frequency of 48 MHz. However, the default values are incorrect.

#### Workaround using Rev B and Rev D

For a 48 MHz PLL clock, set the dividers P=3, N=C0h and M=19h in the SCU\_PLL configuration register.

This is fixed in STR91xFA series devices.

### 2.10 Flash memory read configuration register

#### Description of limitation in Rev B

The Read Configuration register resides in Bank 1 (32KB) of the Flash memory. To write to the register, Bank 1 must be configured as 64KB in the bank size register.

**Fixed in Rev D**. Bit 13 of the Read Configuration register is redefined as a reserved bit, so it is permitted to configure Bank 1 as 32KB.

# 2.11 ISP programming speed

#### **Description of limitation in Rev B**

STR91xF devices contain 3 JTAG TAP controllers, which are daisy-chained. In this configuration, the JTAG clock may never exceed 1/8 of the frequency of the CPU clock. This severely limits the speed of programming the Flash memory during JTAG In-System-Programming.

**Fixed in Rev D**. The JTAG TAP for the ARM CPU may now be bypassed and the JTAG clock frequency is no longer limited to 1/8 CPU clock frequency. This is called "Turbo Mode" and JTAG clock can now equal CPU clock during Flash programming

See STR910 Flash Memory Programming Reference Manual.

### 2.12 Flash memory device security

#### Description of limitation in Rev B