Эти новые высокопроизводительные, малопотребляющие устройства произведены по передовой CMOS технологии компании ISSI и обеспечивают время доступа к данным за 12 нс при работе в автомобильном диапазоне температур от -40°C до +125°C

Когда управляющий вывод обращения к микросхеме CS# (Chip Select) находится в высоком состоянии (обращение запрещено) устройство переходит в режим ожидания, при котором мощность потребления снижается до минимума с поддержанием на входах КМОП-уровней напряжения. Каскадное включение нескольких запоминающих устройств существенно облегчается при помощи управляющих выводов разрешения обращения к микросхеме (CS#) и разрешения выхода (OE#). Активное низкое состояние управляющего вывода разрешения записи WE# контролирует запись и чтение данных. Блок управления вводом/выводом обеспечивает независимый доступ к старшему (UB#) и младшему (LB#) байтам, позволяя работать как с 8-битными, так и с 16-битными данными.

SRAM является одной из разновидностей памяти с произвольным доступом. Каждый байт (8 бит) или слово (16 бит) данных имеет собственный адрес и доступны произвольным образом. Микросхема SRAM-памяти поддерживает три различных рабочих режима. Каждая функция описана в таблице истинности, приведенной ниже.

Режим ожидания

Устройство переходит в дежурный режим в случае запрещения доступа (вывод CS# в активном высоком состоянии). При этом, линии ввода/вывода (I/O0…I/O15) переходят в высокоимпедансное состояние. В этом режиме, поддержание на входах устройства КМОП-уровней напряжения обеспечит максимальную экономию энергии.

Режим записи

Операция записи в память активируется установкой на управляющих выводах CS# и WE# активного низкого состояния. При этом, линии ввода/вывода (I/O0…I/O15) переходят в режим ввода данных. Выходные буферы закрыты в течение этого времени даже если на управляющем выводе OE# установлен низкий активный уровень. Поочередная установка на выводах UB# и LB# активного низкого уровня сигнала позволяет осуществлять побайтную запись данных. Младший байт (LB#) данных переносится с линий ввода/вывода (I/O0…I/O7), а старший байт (UB#) с линий ввода/вывода (I/O8…I/O15) в область памяти, заданную линиями адресации A0…A20.

Режим чтения

Операция чтения данных активируется установкой на управляющем выводе CS# низкого, а на выводе WE# высокого активного состояния. При установке на управляющем выводе OE# низкого логического уровня, выходные буферы включаются для выдачи данных. Прием любых входных сигналов на линиях ввода/вывода в режиме чтения не допускается. Возможность побайтного чтения данных из памяти при помощи управляющих выводов UB# и LB# реализована по схеме, аналогичной операции записи. В режиме чтения данных выходные буферы могут быть отключены установкой на линии OE# высокого логического уровня. В этом случае, внутренняя схема продолжает работу в режиме чтения, а линии ввода/вывода переходят в высокоимпедансное состояние. Поскольку устройство остается в режиме чтения, ток потребления будет соответствовать рабочему уровню потребления.

Процесс включения питания

Устройство интегрирует датчик напряжения, который контролирует процесс включения питания схемы. После того, как на линии питания VDD стабилизируется необходимый уровень напряжения, устройству потребуется 150 мкс (Power-Up Time — tPU), что бы завершить процесс включения питания внутренней схемы. Как только процесс включения питания завершен — устройство готово к нормальной работе.

Таблица истинности

| Режим | CS# | WE# | OE# | LB# | UB# | I/O0-I/O7 | I/O8-I/O15 | ICC |

|---|---|---|---|---|---|---|---|---|

| Доступ запрещен | H | X | X | X | X | High-Z | High-Z | ISB1, ISB2 |

| Выход отключен | L | H | H | L | L | High-Z | High-Z | ICC |

| L | H | H | H | L | High-Z | High-Z | ||

| Чтение | L | H | L | L | H | DOUT | High-Z | ICC |

| L | H | L | H | L | High-Z | DOUT | ||

| L | H | L | L | L | DOUT | DOUT | ||

| Запись | L | L | X | L | H | DIN | High-Z | ICC |

| L | L | X | H | L | High-Z | DIN | ||

| L | L | X | L | L | DIN | DIN |

Легенда:

H — активный высокий уровень сигнала

L — активный низкий уровень сигнала

X — не определен

High-Z — высокоимпедансное состояние

DOUT — выход данных

DIN — вход данных

ISB1, ISB2, ICC — в соответствии с технической документацией

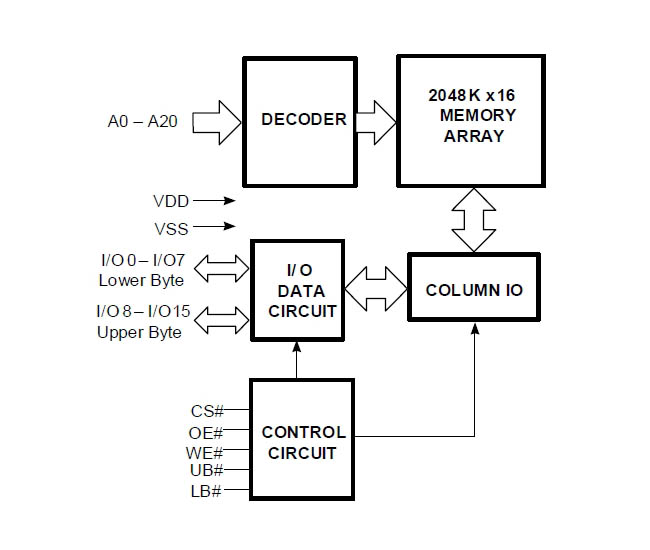

Внутренняя архитектура IS61WV204816/IS64WV204816 |

Отличительные особенности:

- Высокая скорость доступа: 10 нс (для версий в коммерческом и промышленном исполнении- IS61WV204816) и 12 нс (для версии в автомобильном исполнении — IS64WV204816)

- Высокопроизводительная, малопотребляющая CMOS технология

- Несколько линий питания и земли в центральной части корпуса для лучшей электромагнитной совместимости

- Простой способ каскадного включения нескольких микросхем памяти при помощи управляющих выводов CS# и OE#

- Входы и выходы совместимы с TTL-уровнями сигналов

- Единое напряжение питания: от 2.4 В до 3.6 В

- Независимый доступ к старшему и младшему байтам данных

- Диапазон рабочих температур:

- Коммерческий (IS61WV204816): от 0°C до +70°C (минимальное время записи/чтения: 10 нс)

- Промышленный (IS61WV204816): от -40°C до +85°C (минимальное время записи/чтения: 10 нс)

- Автомобильный (IS64WV204816): от -40°C до +125°C (минимальное время записи/чтения: 12 нс)

- Доступные корпуса:

- 48-выводной mini BGA (6 мм х 6 мм)

- 48-выводной TSOP (Type I)

Область применения:

- Сетевые устройства хранения данных

- Инфраструктура проводных сетей

- Компьютерная периферия

- Многофункциональные периферийные устройства

- Серверы

- Промышленная автоматика

- Беспроводные маршрутизаторы

- преобразователи мощности

Запросить образцы, средства разработки или техническую поддержку.

Связанные компоненты

IS61WV204816BLL, 23.06.2016

IS61WV204816BLL, 23.06.2016Быстродействующая асинхронная статическая RAM-память объемом 32 Мбит с напряжением питания 3.3 В

IS64WV204816BLL, 23.06.2016

IS64WV204816BLL, 23.06.2016Быстродействующая асинхронная статическая RAM-память объемом 32 Мбит с напряжением питания 3.3 В

|

Автор документа: Жанна Свирина

, http://www.gaw.ru" |

Дата публикации: 23.06.2016 Дата редактирования: 23.06.2016 |

| Кол-во просмотров 598 | |