Плата MAX 10 NEEK оснащена дисплеем с многоточечным сенсорным экраном, облегчающим процесс разработки и отладки приложений для процессора Nois II, реализованного в энергонезависимой ПЛИС семейства MAX 10

Компания Altera Corporation объявила о доступности второго поколения отладочных наборов для встраиваемого процессора Nios® II (Nios II Embedded Evaluation Kit – NEEK), программно реализованного в энергонезависимой ПЛИС FPGA семейства MAX® 10. Плата MAX 10 NEEK представляет собой многофункциональную платформу, позволяющую разработчикам встраиваемых приложений легко и быстро изучить возможности конфигурируемого процессора Nios II, выполненного на базе энергонезависимой ПЛИС. MAX 10 NEEK является результатом совместной разработки Altera и партнера компании по инструментальным средствам — Terasic.

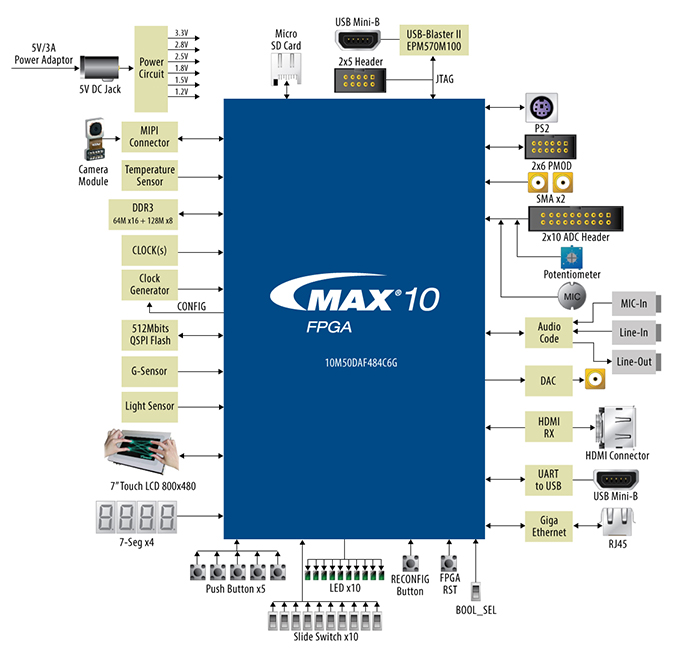

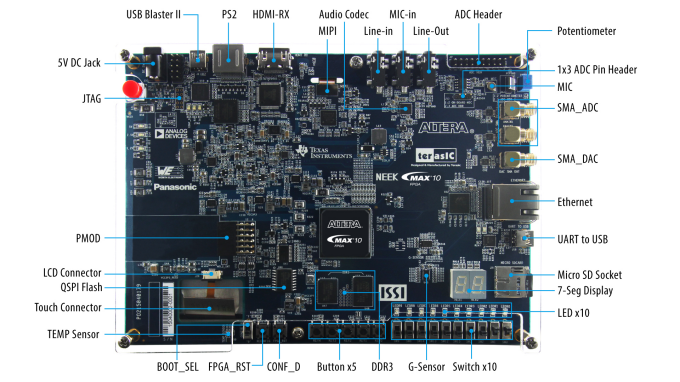

Оценочный комплект MAX 10 NEEK включает плату на базе ПЛИС FPGA семейства MAX 10 и 7-дюймовый дисплей с сенсорным 5-точечным multi-touch экраном. Разработчики встраиваемых систем могут выбрать любой пример приложения из представленного набора демонстрационных базовых проектов, включающий функции сетевых соединений, обработки аудио/видео сигналов и изображений, и запустить его одним касанием пальца. Широкие функциональные возможности платы позволяют реализовать расширенный человеко-машинный интерфейс (HMI), систему машинного зрения, систему мониторинга и контроля благодаря встроенной 8-мегапиксельной MIPI CSI-2 камере, интерфейсу HDMI, датчикам влажности, освещенности и температуре, 3-осевому акселерометру и встроенному микрофону. Подробная информация о оценочном наборе MAX 10 NEEK, в том числе демонстрационные видеоролики, примеры проектов, техническая документация и код для заказа, доступна по адресу www.altera.com/neek.

Блок-диаграмма MAX 10 NEEK |

Внешний вид платы MAX 10 NEEK |

Сочетание программно реализованного процессора Nios II и программируемой логической схемы MAX 10 с интегрированной FLASH-памятью дает ряд преимуществ по сравнению с традиционными микроконтроллерными решениями, включая возможность пользовательской конфигурации системы, защиту от возможного снятия с производства и функцию аппаратного ускорения для обработки данных в реальном масштабе времени. Свободно конфигурируемая система на базе процессора Nios II и ПЛИС FPGA, позволяет разработчикам создать решение, в точности соответствующее требованиям приложения, что невозможно достичь, используя ограниченный набор периферии стандартного микроконтроллера. Процессор Nios II обеспечивает беспрецедентную гибкость применения в недорогих, работающих в реальном масштабе времени и критических с точки зрения безопасности (DO-254) системах. Подробная информация и программно реализованном процессоре Nois II, используемом в энергонезависимых ПЛИС FPGA, доступна по адресу www.altera.com/neek.

MAX 10 предлагают революционное решение в области энергонезависимых ПЛИС, интегрируя два независимых блока конфигурационной FLASH-памяти, а также блоки аналоговой и цифровой обработки сигналов в компактных, недорогих программируемых логических устройствах с минимальным временем конфигурации. ПЛИС FPGA семейства MAX 10 находятся в серийном производстве.

Опытные образцы доступны для заказа в ООО «Гамма Плюс»

- тел.: (812) 320-40-53

- факс: (81378) 3-54-77

- info@icgamma.ru

- www.icgamma.ru

|

Автор документа: Антон Любтеев

, http://www.icgamma.ru" |

Дата публикации: 26.08.2015 Дата редактирования: 27.08.2015 |

| Кол-во просмотров 1368 | |