# **Product Family Specification**

VTI Automotive Digital Accelerometer Platform SCA8X0 / 21X0 / 31X0 Accelerometers

## **TABLE OF CONTENTS**

|                                          | e of Contents                                                                                                                                                                                                                                                                         | 2                          |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Gene                                     | eral Description                                                                                                                                                                                                                                                                      | 5                          |

| 1.1                                      | Introduction                                                                                                                                                                                                                                                                          | 5                          |

| 1.2                                      | Features                                                                                                                                                                                                                                                                              | 5                          |

| 1.3                                      |                                                                                                                                                                                                                                                                                       |                            |

|                                          | ••                                                                                                                                                                                                                                                                                    |                            |

| 1.4                                      | Functional Description                                                                                                                                                                                                                                                                |                            |

|                                          | .4.1 Sensing element                                                                                                                                                                                                                                                                  |                            |

|                                          | .4.3 Capacitance to voltage conversion                                                                                                                                                                                                                                                |                            |

|                                          | .4.4 Analog to digital conversion                                                                                                                                                                                                                                                     |                            |

|                                          | .4.5 Signal conditioning and filtering                                                                                                                                                                                                                                                |                            |

| 1.4                                      | .4.6 Temperature measurement                                                                                                                                                                                                                                                          |                            |

| 1.4                                      | .4.7 Memory                                                                                                                                                                                                                                                                           | 7                          |

|                                          | .4.8 SPI                                                                                                                                                                                                                                                                              |                            |

|                                          | .4.9 Self diagnostics                                                                                                                                                                                                                                                                 |                            |

|                                          | .4.10 Power supply interface                                                                                                                                                                                                                                                          |                            |

| 1.4                                      | .4.11 Factory calibration                                                                                                                                                                                                                                                             | /                          |

| 2 O <sub>l</sub>                         | peration Modes                                                                                                                                                                                                                                                                        | 8                          |

| 2.1                                      | Measurement mode                                                                                                                                                                                                                                                                      | 8                          |

| 2.2                                      |                                                                                                                                                                                                                                                                                       |                            |

|                                          | •                                                                                                                                                                                                                                                                                     |                            |

| 2.3                                      |                                                                                                                                                                                                                                                                                       |                            |

|                                          | .3.1 Memory self-diagnostic                                                                                                                                                                                                                                                           |                            |

|                                          | .3.2 Signal path self-diagnostic                                                                                                                                                                                                                                                      |                            |

|                                          | 2.3.2.2 SCA21X0 and SCA31X0 – multi axis accelerometers                                                                                                                                                                                                                               |                            |

|                                          |                                                                                                                                                                                                                                                                                       |                            |

| 2.4                                      |                                                                                                                                                                                                                                                                                       |                            |

| 2.5                                      | • •                                                                                                                                                                                                                                                                                   |                            |

| 2.6                                      | Recommended operation sequence                                                                                                                                                                                                                                                        | 10                         |

| 2.7                                      | Recommended procedures or optional features                                                                                                                                                                                                                                           | 11                         |

| 2.7                                      | .7.1 SCA8x0/SCA21x0/SCA31x0                                                                                                                                                                                                                                                           |                            |

|                                          | 2.7.1.1 Read back procedure                                                                                                                                                                                                                                                           | 11                         |

|                                          |                                                                                                                                                                                                                                                                                       |                            |

|                                          | 2.7.1.2 Checksum during operation                                                                                                                                                                                                                                                     | 11                         |

|                                          | 2.7.1.3 Saturated data                                                                                                                                                                                                                                                                | 11<br>11                   |

|                                          | 2.7.1.3 Saturated data                                                                                                                                                                                                                                                                | 11<br>11<br>11             |

|                                          | 2.7.1.3 Saturated data                                                                                                                                                                                                                                                                | 11<br>11<br>11             |

| 2.7                                      | 2.7.1.3 Saturated data 2.7.1.4 Noiseless output 2.7.1.5 Component ID 7.2 SCA8x0                                                                                                                                                                                                       | 11<br>11<br>11<br>11       |

| 2.7                                      | 2.7.1.3 Saturated data 2.7.1.4 Noiseless output 2.7.1.5 Component ID 7.2 SCA8x0 2.7.2.1 Mass deflection during operation                                                                                                                                                              | 11<br>11<br>11<br>11<br>11 |

| 2.7                                      | 2.7.1.3 Saturated data 2.7.1.4 Noiseless output 2.7.1.5 Component ID 7.2 SCA8x0 2.7.2.1 Mass deflection during operation 2.7.2.2 Monitor acceleration data during mass deflection                                                                                                     | 1111111111                 |

| 2.7                                      | 2.7.1.3 Saturated data 2.7.1.4 Noiseless output 2.7.1.5 Component ID 2.7.2 SCA8x0 2.7.2.1 Mass deflection during operation 2.7.2.2 Monitor acceleration data during mass deflection                                                                                                   | 11111111                   |

| 2.1<br>3 <b>A</b> 0<br>3.1               | 2.7.1.3 Saturated data 2.7.1.4 Noiseless output 2.7.1.5 Component ID 2.7.2 SCA8x0 2.7.2.1 Mass deflection during operation 2.7.2.2 Monitor acceleration data during mass deflection  ddressing Space  Output registers                                                                | 11111111                   |

| 2.7<br><b>3 Ac</b><br><b>3.1</b><br>3.7  | 2.7.1.3 Saturated data 2.7.1.4 Noiseless output 2.7.1.5 Component ID 7.2 SCA8x0 2.7.2.1 Mass deflection during operation 2.7.2.2 Monitor acceleration data during mass deflection  addressing Space  Output registers 1.1 X axis acceleration output                                  | 11111111                   |

| 2.5<br><b>3 A</b> 0<br><b>3.1</b><br>3.1 | 2.7.1.3 Saturated data 2.7.1.4 Noiseless output 2.7.1.5 Component ID 2.7.2 SCA8x0 2.7.2.1 Mass deflection during operation 2.7.2.2 Monitor acceleration data during mass deflection  addressing Space  Output registers 1.1 X axis acceleration output 3.1.1.1 X_LSB                  | 11111111121212             |

| 2.5<br>3 Ac<br>3.1<br>3.4                | 2.7.1.3 Saturated data 2.7.1.4 Noiseless output 2.7.1.5 Component ID 2.7.2 SCA8x0 2.7.2.1 Mass deflection during operation 2.7.2.2 Monitor acceleration data during mass deflection  addressing Space  Output registers  1.1 X axis acceleration output 3.1.1.1 X_LSB. 3.1.1.2 X_MSB. | 11111112121212             |

| 2.5<br>3 Ac<br>3.1<br>3.4                | 2.7.1.3 Saturated data 2.7.1.4 Noiseless output 2.7.1.5 Component ID 2.7.2 SCA8x0 2.7.2.1 Mass deflection during operation 2.7.2.2 Monitor acceleration data during mass deflection  addressing Space  Output registers 1.1 X axis acceleration output 3.1.1.1 X_LSB                  | 1111111212121213           |

|             | · ·                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -           |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | <del>-</del>                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | ·                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | o,                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.1.        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.1.        | · · · · · · · · · · · · · · · · · · ·    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.2         |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| _           | g , ,                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.2.        | 2 Reset Register (RESET)                 | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.3         | Identification registers                 | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.3.        | 1 Revision ID (REVID)                    | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.3.        | 2 Component ID (ID)                      | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

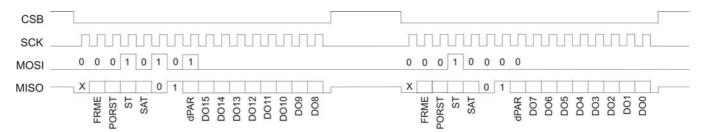

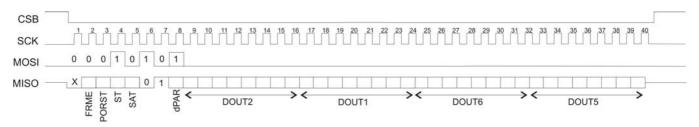

| SP          | Interface                                | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | ·                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | ,                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.2.        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.2.        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.2.        | 8 Output data                            | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Ele         | ctrical Characteristics                  | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| E 4         | Aboolute maximum ratings                 | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>3.</b> 1 | •                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.2         | Power Supply                             | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

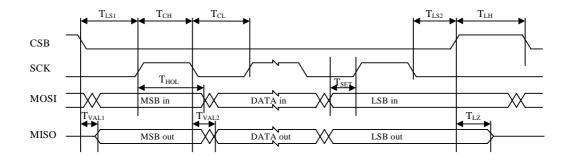

| 5.3         | Digital I/O Specification                | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.3.        | 2 AC Characteristics                     | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Δη          | nlication information                    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| -           |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

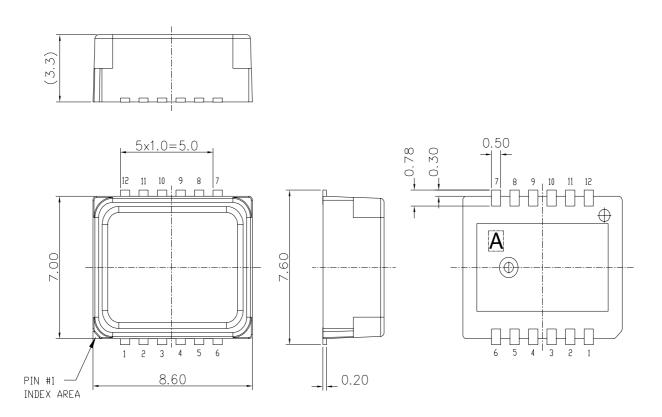

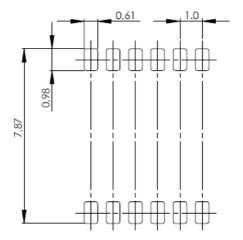

| 6.1         | Package dimensions                       | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.2         | Output to Angle Conversion               | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.2         | . •                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | <u> </u>                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

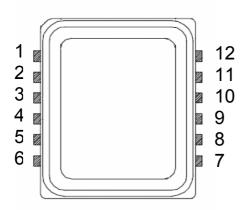

| 6.4         | Pin Description                          | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

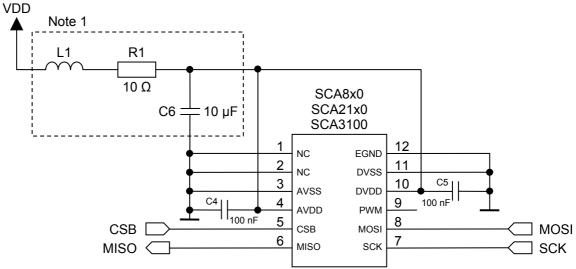

| 6.5         | Recommended circuit diagram              | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

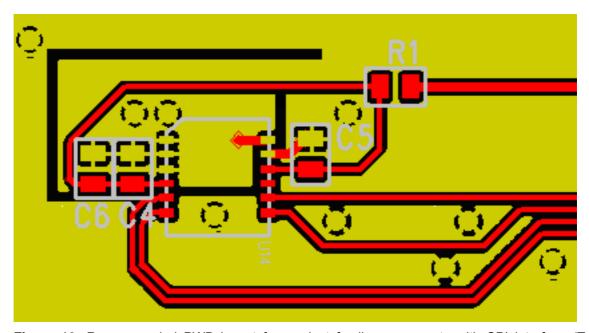

| 6.6         | Recommended PWB layout                   | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.7         | Assembly instructions                    | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 3.1. 3.3 3.1. 3.3 3.1. 3.1. 3.2. 3.2. 3. | 3.2.1 Control Register (CTRL) 3.2.2 Reset Register (RESET) 3.3 Identification registers 3.3.1 Revision ID (REVID) 3.3.2 Component ID (ID)  SPI Interface  4.1 Output of Acceleration Data 4.1.1 Register read operation 4.1.2 Decremented register read operation 4.1.3 MOSI data of SPI commands  4.2 Error Conditioning 4.2.1 FRRME-bit 4.2.2 PORST-bit. 4.2.3 ST-bit (SCA21X0 / 3100) 4.2.4 SAT-bit (SCA21X0 / 3100) 4.2.5 aPAR-bit (SCA21X0 / 3100) 4.2.6 dPAR-bit 4.2.7 Fixed bits 4.2.8 Output data 5 Electrical Characteristics 5.1 Absolute maximum ratings 5.2 Power Supply 5.3 Digital I/O Specification 5.3.1 DC Characteristics 5.3.2 AC Characteristics 5.3.1 DC Characteristics 6.4 Pin Description 6.5 Recommended PWB layout |

|   | 6.8 | Tape and reel specifications | 34  |

|---|-----|------------------------------|-----|

| 7 | Co  | ontact Information           | .35 |

| 8 | Do  | ocument Change Control       | 36  |

#### **General Description**

#### 1.1 Introduction

VTI Automotive Digital Accelerometer Platform is an accelerometer product concept based on VTI capacitive 3D-MEMS technology. The VTI ADP platform integrates high accuracy micromechanical acceleration sensing together with a flexible SPI digital interface. The products within the platform range from single axis accelerometers into two or three axis accelerometers. Dual Flat Lead (DFL) housing of the component guarantees robust operation over the product lifetime.

The products are designed, manufactured and tested for high stability, reliability and quality requirements of automotive applications. The accelerometers have extremely stable output over wide range of temperature, humidity and mechanical noise. The components are qualified against AEC-Q100 standard and have several advanced self diagnostics features. The DFL housing is suitable for SMD mounting and the component is compatible with RoHS and ELV directives.

This Product Family Specification describes the VTI Automotive Digital Accelerometer Platform common characteristics and how to operate with the products. Detail product specification is described in individual data sheets of each product.

#### 1.2 Features

Standard features of the VTI Automotive Digital Accelerometer Platform

- · Single, dual or three axis acceleration measurement

- SPI digital interface

- 3.3V supply voltage

- Enhanced self diagnostics features

- Internal temperature sensor

- Size 7.6 x 3.3 x 8.6 mm (w x h x l)

- RoHS compliant Dual Flat Lead (DFL) plastic package suitable for lead free soldering process and SMD mounting

- Package, pin-out and SPI protocol compatible within the product family

- Proven capacitive 3D-MEMS technology

- · Qualified according to AEC-Q100 standard

Main characteristics of each product within the product family are listed in Table 1 below.

**Table 1: Digital platform summary**

| Туре        | Measuring directions |                           |  |

|-------------|----------------------|---------------------------|--|

| SCA810-D01  | X                    | Single axis Accelerometer |  |

| SCA820-D03  | Z                    | Single axis Accelerometer |  |

| SCA830-D05  | Υ                    | Single axis Accelerometer |  |

| SCA2100-D01 | X, Y                 | Dual axis Accelerometer   |  |

| SCA2110-D03 | X, Z                 | Dual axis Accelerometer   |  |

| SCA2120-D05 | Y, Z                 | Dual axis Accelerometer   |  |

| SCA3100-D01 | X, Y, Z              | Three axis Accelerometer  |  |

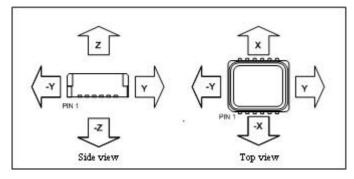

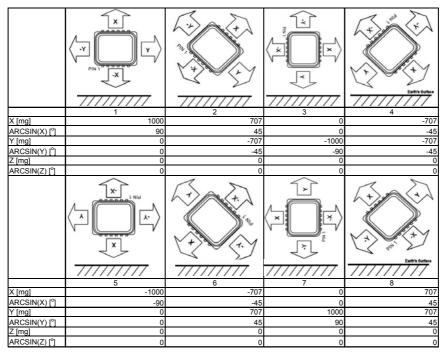

Figure 1: Measurement directions

#### 1.3 Typical applications

VTI Automotive Digital Accelerometer Platform is targeted to automotive applications with high stability requirements. Typical applications include but are not limited to

- Electronic Stability Control (ESC)

- Hill Start Assist (HSA)

- Electronic Parking Brake (EPB)

- Roll Over

- Active Suspension

- Inclination

- Industrial applications

#### 1.4 Functional Description

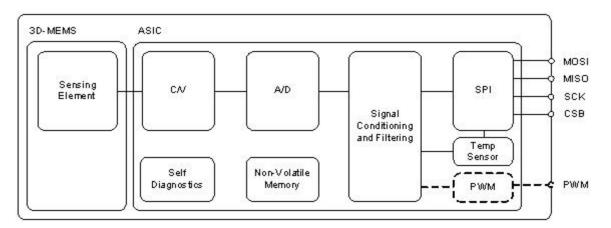

Basic product concept of the VTI Automotive Digital Accelerometer Platform is a two chip solution consisting of a single sensing element and one ASIC inside a pre-molded 12-pin housing. The interface to the application is a four wire digital SPI interface. In single axis products there is also Pulse Width Modulation output available. In addition to the supply voltage filtering the component does not require any other components to be connected to the device.

Block diagram of SCA8X0/SCA21X0/31X0

#### 1.4.1 Sensing element

The sensing element of the product is manufactured by using VTI Technologies proprietary bulk 3D-mems process enabling a robust, stable and low noise capacitive sensor. Depending on the product type and measurement direction the sensing element type and orientation inside the housing can vary. Single axis products are equipped with single axis sensing elements and multi axis products are equipped with multi axis sensing elements.

#### 1.4.2 Interface IC

The main functional blocks of the interface ASIC are the following:

#### 1.4.3 Capacitance to voltage conversion

The acceleration is causing a capacitance change inside the sensing element. The capacitance change can be detected by the ASIC analog interface. The capacitance information is converted into an analog voltage that can be further processed easily inside the ASIC.

#### 1.4.4 Analog to digital conversion

Analog voltage information is amplified and filtered and converted into digital information for signal processing inside the ASIC.

#### 1.4.5 Signal conditioning and filtering

The block filters and conditions the measurement information needed for the application

### 1.4.6 Temperature measurement

The accelerometers contain a temperature sensor for temperature compensation purposes and for use in the application.

#### 1.4.7 Memory

Factory programmed calibration values are stored in a non-volatile memory

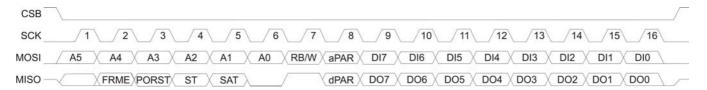

#### SPI 1.4.8

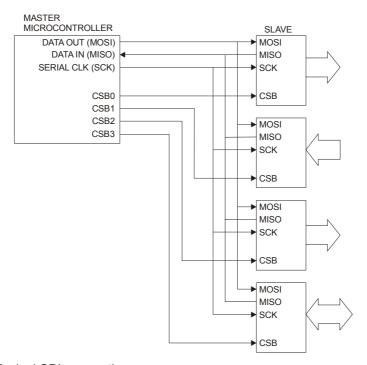

SPI interface is a simple four wire interface for communication between the component and the application micro controller.

#### Self diagnostics 1.4.9

The VTI Automotive Digital Platform contains several enhanced diagnostics features to allow timely and robust failure detection.

#### 1.4.10 Power supply interface

The products are equipped with separate power and ground pins for analog and digital functionality to allow high accuracy measurement.

#### 1.4.11 Factory calibration

VTI Automotive Digital Platform accelerometers are factory calibrated. No separate calibration is required in the application. Trimmed parameters during production include sensitivity, offset and frequency response. Calibration parameters are stored during the manufacturing of the part inside a non-volatile memory. The parameters are read automatically from the internal non-volatile memory during the startup of the sensor after power on.

#### 2 **Operation Modes**

#### 2.1 Measurement mode

After the startup the acceleration data is immediately available through the SPI registers. There is no need to initialize the accelerometer before starting to use of it. If the application is requiring monitoring of the correctness of the operation there are several options available to monitor the operation status.

### 2.2 Temperature output

The devices include a temperature measurement function. Temperature data can be read through the SPI interface. Temperature measurement is not calibrated for absolute accuracy. If absolute accuracy is needed, it can be achieved through measuring the temperature value in two temperature points in final application and storing them as a calibration value and calculating the absolute temperature value by using the two points.

#### **Self-diagnostic functions**

VTI Automotive Digital Accelerometer Platform has a set of built-in self-diagnostic functions to support the application fail safety. The diagnostic functions cover the accelerometer sensing element functionality, accelerometer internal operation and signal path functionality

### 2.3.1 Memory self-diagnostic

Factory calibrated values of the accelerometer are stored in a non-volatile memory. The calibrated values are read during the device power on into volatile registers that control the operation of the device. During the startup of the device the calculated sum of non-volatile registers is compared to the factory calibrated value. The test is done automatically after supplies are set on, after any reset state of component and after return from power-down mode. Test can also be started by a CTRLregister command.

#### Signal path self-diagnostic

#### 2.3.2.1 SCA8X0 - single axis accelerometers

Sensor element and signal path is tested by deflecting the proof mass of the sensing element to both directions over a predefined dynamic range. The test is done automatically during start-up and it can be repeated by a CTRL-register command. The result of the test is a momentary mass deflection seen in the output of the device. During the test the accelerometer performs a comparison of the deflection result to a pre-defined threshold value. When the needed dynamics have been detected the device will return the result of a passed test in a register. By following the output of the device on SPI interface it is possible to detect failures through the signal path.

#### SCA21X0 and SCA31X0 - multi axis accelerometers 2.3.2.2

#### 2.3.2.2.1 Start-up Self Test (STS)

During the application start up or when the accelerometer is affected by the gravity force only it is possible to detect possible sensing element anomalies by applying a start up self test. The test is done in a following way: a digitally calculated resultant acceleration of x, y and z-axis is compared to predefined threshold value. Test is started by CTRL-register command and it is done once when requested.

#### 2.3.2.2.2 Continuous Self Test (STC)

During device operation the continuous self test is monitoring the sensing element performance. Digitally calculated self-diagnostic function is compared to predefined threshold value. Test is started by CTRL-register command and it is calculated continuously on background until disabled. Possible errors are indicated in an error status register and in SPI frame.

#### 2.4 Power Down mode

For low power applications it is possible to set the accelerometer into power down mode. During the power down mode the power consumption is minimized inside the device. This is achieved by stopping the internal clocks and resetting the control registers of the device. Please refer to the individual device data sheets for detail power consumption figures.

### 2.5 Recommended start-up sequence

For correct device operation there are no specific configuration needed for the device before starting of measuring the acceleration. However if the device detail features are being used the following operations could be made after the powering on the device.

Table 2: SCA8X0 start up sequence

| Item | Procedure                     | Functions                                                                                                                                                                                                  | Check                                                                                                      |

|------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 1    | Set Vdd=3.03.6V               | <ul> <li>Set the<br/>power on to<br/>release part<br/>from reset<br/>and to start<br/>the operation</li> </ul>                                                                                             | -                                                                                                          |

| 2    | Wait 95ms                     | <ul> <li>During the first 95ms the part is performing the memory read and self-diagnostics.</li> <li>Possible signal path self-diagnostic test is carried out.</li> <li>Settling of signal path</li> </ul> |                                                                                                            |

| 3    | Read CTRL-register            | Check the self-test pass status                                                                                                                                                                            | <ul><li>CTRL.ST=0</li><li>SPI fixed bits</li><li>dPAR, data parity</li></ul>                               |

| 4    | Read STATUS-register          | <ul> <li>Check the<br/>memory<br/>checksum<br/>pass status</li> </ul>                                                                                                                                      | <ul> <li>STATUS.CSMERR=0</li> <li>SPI fixed bits</li> <li>SPI FRME=0</li> <li>dPAR, data parity</li> </ul> |

| 5    | Write CTRL=0000 0000          | <ul> <li>After device<br/>power on set<br/>PORST=0 to<br/>be able to<br/>detect any<br/>future<br/>occurring<br/>power<br/>failures</li> </ul>                                                             | <ul><li>SPI fixed bits</li><li>SPI FRME=0</li></ul>                                                        |

| 6    | Read X_MSB, X_LSB – registers | Start reading<br>the<br>acceleration<br>data                                                                                                                                                               | <ul><li>SPI fixed bits</li><li>SPI FRME=0</li><li>SPI PORST=0</li><li>dPAR, data parity</li></ul>          |

Table 3: SCA21X0 and SCA31X0 start up sequence

| Item | Procedure                                                                         | Functions                                                                                                                        | Check                                                                                                                                                                                 |

|------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Set Vdd=3.03.6V                                                                   | <ul> <li>Release part from<br/>reset</li> </ul>                                                                                  | -                                                                                                                                                                                     |

| 2    | Wait 35ms                                                                         | <ul><li>Memory reading<br/>and self-diagnostic</li><li>Settling of signal<br/>path</li></ul>                                     | -                                                                                                                                                                                     |

| 3    | Read INT_STATUS                                                                   | <ul> <li>Acknowledge for<br/>possible saturation<br/>(SAT-bit)</li> <li>Checksum pass<br/>detected from SPI<br/>frame</li> </ul> | <ul><li>SPI fixed bits</li><li>SPI ST=0</li></ul>                                                                                                                                     |

| 4    | Write<br>CTRL=00001010 (a)<br>or<br>CTRL=00001000 (b)<br>or<br>CTRL=000000000 (c) | <ul><li>Set PORST=0 (abc)</li><li>Start STC (ab)</li><li>Start STS (a)</li></ul>                                                 | <ul><li>SPI fixed bits</li><li>SPI FRME=0</li><li>SPI ST=0</li><li>SPI SAT=0</li></ul>                                                                                                |

| 5    | Wait 10ms                                                                         | STS calculation                                                                                                                  | _                                                                                                                                                                                     |

| 6    | Read CTRL                                                                         | <ul> <li>Check that STC is on, if enabled</li> <li>Check that STS is over if enabled</li> </ul>                                  | <ul> <li>CTRL.ST=1</li> <li>CTRL.ST_CFG=0</li> <li>SPI fixed bits</li> <li>SPI FRME=0</li> <li>SPI PORST=0</li> <li>SPI ST=0</li> <li>SPI SAT=0</li> <li>dPAR, data parity</li> </ul> |

| 7    | Read Z_MSB, Z_LSB,<br>Y_MSB, Y_LSB,<br>X_MSB, X_LSB                               | Read acceleration data                                                                                                           | <ul> <li>SPI fixed bits</li> <li>SPI FRME=0</li> <li>SPI PORST=0</li> <li>SPI ST=0</li> <li>SPI SAT=0</li> <li>dPAR, data parity</li> </ul>                                           |

## 2.6 Recommended operation sequence

Table 4: Reading of the acceleration data

| Item | Procedure                            | Functions                                                     | Check                                                                                                                                       |

|------|--------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Read acceleration data               | Desired x, y, or/and z-data                                   | <ul> <li>SPI fixed bits</li> <li>SPI FRME=0</li> <li>SPI PORST=0</li> <li>SPI ST=0</li> <li>SPI SAT=0</li> <li>dPAR, data parity</li> </ul> |

| 2    | Repeat item 1 (N-1) times            | Noise averaging                                               | - ' '                                                                                                                                       |

| 3    | Calculate average (AVE) of N-samples | Noise averaging                                               | -                                                                                                                                           |

| 4    | Read acceleration data               | Desired x, y,<br>or/and z-data<br>(one read<br>before sending | <ul><li>SPI fixed bits</li><li>SPI FRME=0</li><li>SPI PORST=0</li></ul>                                                                     |

| Item | Procedure                   | Functions                                    | Check                                                                  |

|------|-----------------------------|----------------------------------------------|------------------------------------------------------------------------|

|      |                             | AVE forward<br>to check SPI<br>failure bits) | <ul><li>SPI ST=0</li><li>SPI SAT=0</li><li>dPAR, data parity</li></ul> |

| 5    | Send calculated AVE forward | -                                            | -                                                                      |

| 6    | Jump back to item 2         | -                                            | -                                                                      |

For detailed SPI failure bit information see chapter 4.2 Error Conditioning

#### 2.7 Recommended procedures or optional features

Product family components have different features, which are not required during normal operation. However, they are recommended in some cases if they are seen important from system perspective.

#### 2.7.1 SCA8x0/SCA21x0/SCA31x0

#### 2.7.1.1 Read back procedure

It is recommended to read back every write command to compare read data to the write command. This way it is detected very unlikely failures in MCU, in SPI wiring, in SPI interface, in system clock or inside state machine.

#### 2.7.1.2 Checksum during operation

Checksum is calculated for component register values that control the operation of product. Data is read from non-volatile memory to these registers during start-up and checksum is calculated automatically. It is possible to repeat checksum calculation during normal operation by CTRL register command and test result can be seen from STATUS register (see more info in 3.2.1 and 3.1.6). In multi-axis products test result can be seen also from SPI frame. By repeating checksum during normal operation, it is possible to detect very unlikely intermittent or static bit failures in register map.

#### 2.7.1.3 Saturated data

Output data saturates to predefined value if product dynamic range is exceeded. If output data has been saturated it should be considered invalid and it should not be used for system controlling. Output data saturation can also be indication of some very unlike component failure.

#### 2.7.1.4 Noiseless output

Valid acceleration output includes always some noise. If output data is constant, it can be indication of system error and data is not valid anymore. Therefore it is useful to monitor noise or deviation of output data.

#### 2.7.1.5 Component ID

Each product family component type has unique identification number, which is stored to non-volatile memory (see 3.3.2). This number can be used for example in production line to check that correct component is mounted to the system. In some cases it may be used for MCU software controlling.

#### 2.7.2 SCA8x0

#### 2.7.2.1 Mass deflection during operation

Mass deflection self-test is performed automatically to both direction in start-up. Mass deflection can be performed during operation if requested by user. Test is started and direction is controlled

by CTRL register (see more info in 3.2.1). Note that acceleration output data is not valid during test and after test is started to one direction there has to be 50ms wait time before output data is used.

### 2.7.2.2 Monitor acceleration data during mass deflection

Acceleration data can be read out from acceleration output registers during mass deflection self-test in start-up or during operation, in case that test is repeated by the request. Monitoring this data it is possible to determine product frequency response and check product timing properties.

### 3 Addressing Space

Table 5 presents the registers of SCA8X0, SCA21X0 and SCA31X0 products.

Table 5: Register address space

| Addr<br>hex | Name       | Description                                        | Mode<br>(R/RW) |

|-------------|------------|----------------------------------------------------|----------------|

| 00          | REVID      | ASIC revision ID number                            | R              |

| 01          | CTRL       | Control                                            | RW             |

| 02          | STATUS     | Status                                             | R              |

| 03          | RESET      | Reset component                                    | RW             |

| 04          | X_LSB      | X-axis (or Y- or Z-axis in SCA8X0) LSB frame       | R              |

| 05          | X_MSB      | X-axis (or Y- or Z-axis in SCA8X0) MSB frame       | R              |