# MicroConverter, Dual 10-channel 24-Bit ADCs with Embedded 62kB FLASH MCU

# **Preliminary Technical Data**

ADuC845

#### **FEATURES**

#### **High Resolution Sigma-Delta ADCs**

Two Independent ADCs (24-Bit Resolution)

Up to 10 ADC input channels

24-Bit No Missing Codes, Primary ADC

20-Bit rms (17.4 Bit p-p) Effective Resolution @ 60 Hz

Offset Drift 10 nV/°C, Gain Drift 0.5 ppm/°C (Chop enabled)

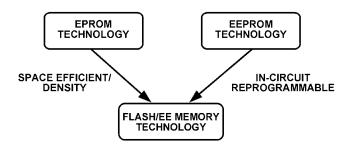

#### Memory

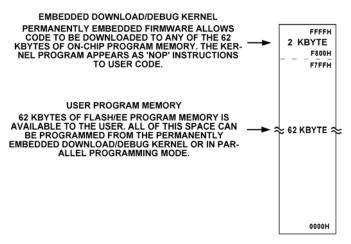

62 Kbytes On-Chip Flash/EE Program Memory

4 Kbytes On-Chip Flash/EE Data Memory

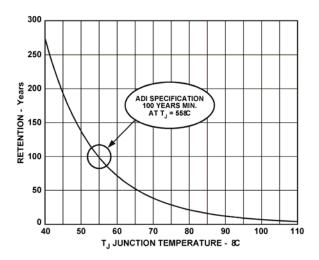

Flash/EE, 100 Year Retention, 100 Kcycles Endurance

3 Levels of Flash/EE Program Memory Security

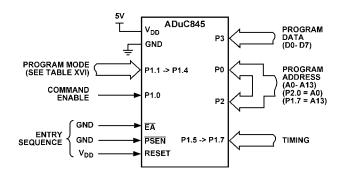

In-Circuit Serial Download (No External Hardware)

High Speed User Download (5 Seconds)

2304 Bytes On-Chip Data RAM

#### 8051-Based Core

8051 Compatible Instruction Set

High Performance Single Cycle Core

32 kHz External Crystal

On-Chip Programmable PLL (12.58 MHz Max)

3 16-Bit Timer/Counter

26 Programmable I/O Lines

11 Interrupt Sources, Two Priority Levels

Dual Data Pointer, Extended 11-Bit Stack Pointer

#### **On-Chip Peripherals**

Internal Power on Reset Circuit

12-Bit Voltage Output DAC

Dual 16-Bit S-D DACs/PWMs

On-Chip Temperature Sensor

**Dual Excitation Current Sources**

Time Interval Counter (Wakeup/RTC Timer)

UART, SPI<sup>®</sup>, and I<sup>2</sup>C<sup>®</sup> Serial I/O

High Speed Baud Rate Generator (incl 115,200)

Watchdog Timer (WDT)

Power Supply Monitor (PSM)

#### **Power**

Normal: 2.3mA Max @ 3.6 V (Core CLK = 1.57 MHz)

Power-Down: 20uA Max with Wakeup Timer Running

Specified for 3 V and 5 V Operation

#### Package and Temperature Range

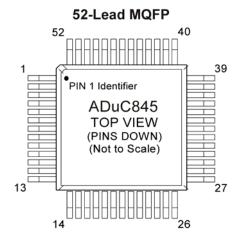

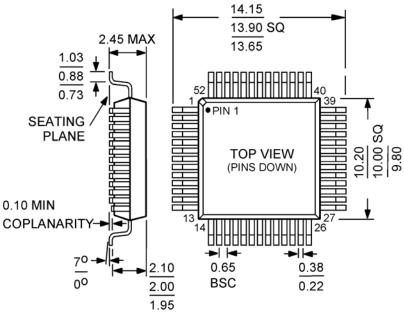

52-Lead MQFP (14 mm x 14 mm), -40°C to +125°C

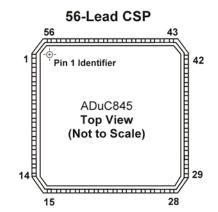

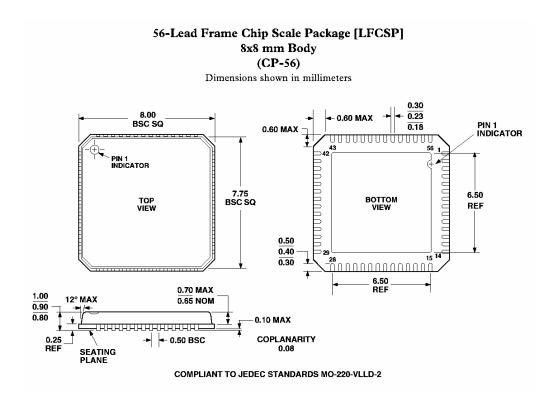

56-Lead CSP (8 mm x 8 mm), -40°C to +85°C

#### APPLICATIONS

Multi channel Sensor monitoring

Industrial/Environmental Instrumentation

WeighScales

Portable Instrumentation, Battery Powered Systems

4-20mA Transmitters

Data Logging

Precision System Monitoring

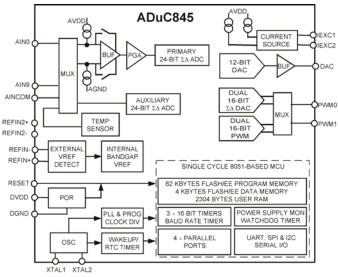

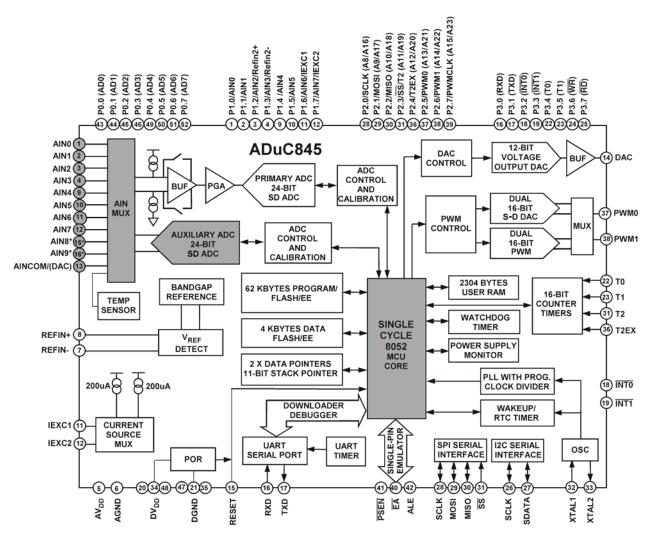

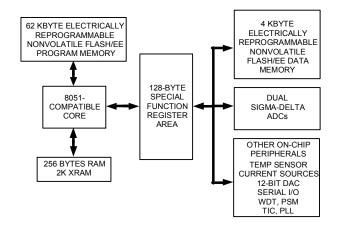

#### FUNCTIONAL BLOCK DIAGRAM

#### REV. PrC

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

Purchase of licensed I<sup>2</sup>C components of Analog Devices or one of its sublicensed Associated Companies conveys a license for the purchaser under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved

### ADuC845

**SPECIFICATIONS**(AVDD = 2.7 V to 3.6 V or 4.75 V to 5.25 V, DVDD = 2.85 V to 3.6 V or 4.75 V to 5.25 V, REFIN(+) = 2.5 V, REFIN(-) = AGND; AGND = DGND = 0 V; XTAL1/XTAL2 = 32.768 kHz Crystal; all specifications T<sub>MIN</sub>, to T<sub>MAX</sub> unless otherwise noted.). Input Buffer On for Primary ADC unless otherwise noted.

| PARAMETER                                          | MIN                  | TYP                             | MAX             | UNITS                                  | CONDITION                                                                                                                                                                                    |

|----------------------------------------------------|----------------------|---------------------------------|-----------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRIMARY ADC <sup>1</sup>                           |                      |                                 |                 |                                        |                                                                                                                                                                                              |

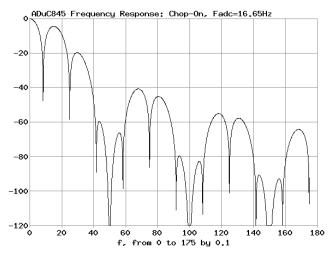

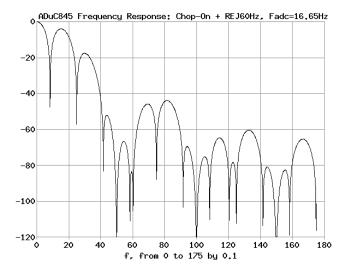

| Conversion Rate                                    | 5.4<br>16.06         | 19.79<br>59.36                  | 105<br>1365     | Hz<br>Hz                               | Chop On (ADCMODE.3 = 0)<br>Chop Off (ADCMODE.3 = 1)                                                                                                                                          |

| No Missing Codes <sup>2</sup>                      | 24 24                | 37.30                           | 1505            | Bits                                   | 19.79Hz Update Rate                                                                                                                                                                          |

| Resolution                                         | 24                   | 13.5                            |                 | Bits Pk-Pk                             | 59.36Hz Update Rate  Range = ± 20mV, 20Hz Update Rate, Chop On                                                                                                                               |

| Output Noise                                       | See Tab              | 13<br>18.5<br>17.4<br>les V, VI | VII & VIII      | Bits Pk-Pk<br>Bits Pk-Pk<br>Bits Pk-Pk | Range = ± 20mV, 59Hz Update Rate, Chop Off<br>Range = ± 2.56V, 20Hz Update Rate, Chop On<br>Range = ± 2.56V, 59.4Hz Update Rate, Chop Off<br>Output Noise varies with selected Update Rates, |

| Integral Non Linearity                             | in A                 | DC Descr<br>±2                  | ription<br>± 15 | ppm of FSR                             | Gain Range and Chop status.  1 LSB <sub>16</sub>                                                                                                                                             |

| Offset Error <sup>3</sup>                          |                      | ± 3                             |                 | μV                                     | Chop On (ADCMODE.3=0)                                                                                                                                                                        |

|                                                    | See t                | ables VII                       | & VIII          | 200                                    | Chop Off (ADCMODE.3=1).  Offset Error is in the order of the noise for the programmed gain and update rate following a calibration.                                                          |

| Offset Error Drift vs. Temp                        |                      | ± 10                            |                 | nV/°C                                  | Chop On (ADCMODE.3=0)                                                                                                                                                                        |

| Full-Scale Error <sup>4</sup>                      |                      | ±200<br>± 10                    |                 | nV/°C<br>μV                            | Chop Off (ADCMODE.3=1)                                                                                                                                                                       |

| Gain Error Drift vs. Temp <sup>5</sup>             |                      | ± 0.5                           |                 | ppm/°C                                 |                                                                                                                                                                                              |

| PRIMARY ADC ANALOG INPUTS                          |                      |                                 |                 |                                        |                                                                                                                                                                                              |

| Differential Input Voltage Ranges <sup>9, 10</sup> |                      |                                 |                 |                                        | GAIN = 1 to 128                                                                                                                                                                              |

| Bipolar Mode (ADC0CON1.5 = $0$ )                   | ± 1.0                | )24 x V <sub>REF</sub>          | /GAIN           | V                                      | V <sub>REF</sub> = REFIN(+) - REFIN(-) or REFIN2(+) -<br>REFIN2(-) (or Int 1.25V Ref)                                                                                                        |

| Unipolar Mode (ADC0CON1.5 = 1)                     | 0 <b>→</b> 1         | .024 x Vr                       | ef/GAIN         | V                                      | V <sub>REF</sub> = REFIN(+) - REFIN(-) or REFIN2(+) -<br>REFIN2(-) (or Int 1.25V Ref)                                                                                                        |

| ADC Range Matching<br>Common Mode DC Rejection     |                      | ± 2                             |                 | μV                                     | AIN=18mV, Chop=On, Buffer=On.                                                                                                                                                                |

| On AIN<br>On AIN                                   | 95                   | 100<br>113                      |                 | dBs<br>dBs                             | @DC, AIN=7.8mV, Range=± 20mV<br>@DC, AIN=1V, Range=± 2.56V                                                                                                                                   |

| Common Mode 50/60Hz Rejection                      |                      | 113                             |                 | uDs                                    | 20Hz Update Rate                                                                                                                                                                             |

| On AIN                                             | 95                   |                                 |                 | dBs                                    | 50/60Hz ± 1Hz, AIN=7.8mV, Range=± 20mV                                                                                                                                                       |

| On AIN                                             | 90                   |                                 |                 | dBs                                    | 50/60Hz ± 1Hz, AIN=1V, Range=± 2.56V<br>59Hz Update Rate                                                                                                                                     |

| On AIN                                             | 95                   |                                 |                 | dBs                                    | 50/60Hz ± 1Hz, AIN=7.8mV, Range=± 20mV                                                                                                                                                       |

| On AIN                                             | 90                   |                                 |                 | dBs                                    | 50/60Hz ± 1Hz, AIN=1V, Range=± 2.56V                                                                                                                                                         |

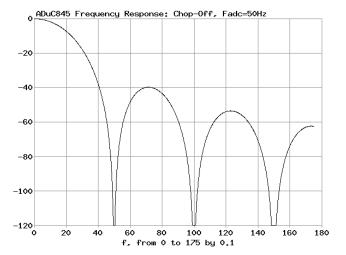

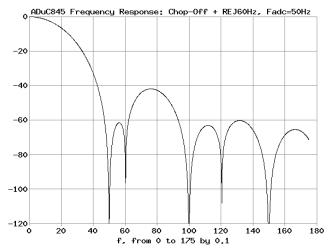

| Normal Mode 50/60 Hz Rejection<br>On AIN           | 60                   |                                 |                 | dBs                                    | 50/60Hz ± 1Hz<br>20Hz Update Rate, Chop On                                                                                                                                                   |

| On AIN                                             | 60                   |                                 |                 | dBs                                    | 59Hz Update Rate, Chop Off                                                                                                                                                                   |

| Analog Input Current <sup>2</sup>                  |                      |                                 | ± 1             | nA                                     | T <sub>MAX</sub> = 85°C, Buffer On                                                                                                                                                           |

|                                                    |                      |                                 | ± 5             | nA                                     | $T_{MAX} = 125$ °C, Buffer On                                                                                                                                                                |

| Analog Input Current Drift                         |                      | ± 5                             |                 | pA/°C                                  | $T_{MAX} = 85$ °C, Buffer On                                                                                                                                                                 |

| Analas Isra (C. m. )                               |                      | ± 15                            |                 | pA/°C                                  | T <sub>MAX</sub> = 125°C, Buffer On                                                                                                                                                          |

| Analog Input Current Analog Input Current Drift    |                      | ± 125<br>± 2                    |                 | nA/V<br>pA/V/°C                        | ± 2.56V Range, Buffer Bypassed<br>Buffer bypassed                                                                                                                                            |

| Absolute AIN Voltage Limits <sup>2</sup>           | $A_{GND} + 0$        |                                 | $AV_{DD}-0.1$   | V V                                    | Ain1-Ain10 and AINCON with Buffer ON (ADC0CON1.6 = 0 & ADC0CON1.7 = 0)                                                                                                                       |

| Absolute AIN Voltage Limits                        | A <sub>GND</sub> - 0 | .03 A                           | $V_{DD} + 0.03$ | V                                      | Ain1-Ain10 and AINCON with Buffer Bypassed (ADC0CON1.6=0, ADC0CON1.7=1)                                                                                                                      |

-2-REV. PrC

# ADuC845

| EXTERNAL REFERENCE INPUTS                                         |                         |                       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------|-------------------------|-----------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFIN(+) to REFIN(-) Voltage                                      | 2.5                     | <b>A</b> 37           | V            | REFIN refers to both REFIN and REFIN2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| REFIN(+) to REFIN(-) Range <sup>2</sup>                           | 1                       | $AV_{DD}$             | V            | REFIN refers to both REFIN and REFIN2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Average Reference Input Current                                   | +/-1                    |                       | μA/V         | Both ADCs Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Average Reference Input Current Drift<br>'NOXREF' Trigger Voltage | +/- 0.1<br>0.3          | 0.65                  | nA/V/°C<br>V | NOXREF (ADCSTAT.4) bit active if Vref<0.3V,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                   |                         |                       |              | and Inactive if Vref>0.65V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Common Mode Rejection                                             |                         |                       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DC Rejection                                                      | 125                     |                       | dB           | @DC, AIN=1V, Range=± 2.56V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 50/60Hz Rejection <sup>2</sup>                                    | 90                      |                       | dB           | 50/60Hz ± 1Hz, AIN=1V, Range=± 2.56V, SF=82<br>REJ60 = 1 (ADCMODE.6 = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Normal Mode Rejection                                             |                         |                       |              | REJ00 - 1 (ADCMODE.0 - 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 50/60 Hz Rejection <sup>2</sup>                                   | 60                      |                       | dB           | 50/60Hz ± 1Hz, AIN=1V, Range=± 2.56V, SF=82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 30/00 Hz Rejection                                                | 00                      |                       | uБ           | REJ60 = 1 (ADCMODE.6 = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ANNI ANNI ANG                                                     |                         |                       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AUXILIARY ADC Conversion Rate                                     | 5.4 19.79               | 105                   | Hz           | Chop On                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Conversion Rate                                                   | 16.06 59.36             | 1365                  | Hz           | Chop Off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| No Missing Codes <sup>2</sup>                                     | 24                      | 1303                  | Bits         | 19.79Hz Update Rate, Chop On                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| No Missing Codes                                                  | 24                      |                       | Bits         | 59.36Hz Update Rate, Chop Off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Resolution                                                        |                         |                       |              | Transfer of the second of the |

|                                                                   | 16                      |                       | Bits Pk-Pk   | Range = $\pm$ 2.56V, 19.79Hz Update Rate, Chop On                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                   | 16                      |                       | Bits Pk-Pk   | Range = $\pm 2.56$ V, 59.36Hz Update Rate, Chop Off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Output Noise                                                      | See Tab                 |                       |              | Output Noise varies with selected Update Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                   | Auxiliary               | ADC                   |              | Output Noise will typically degrade from Chop<br>Enabled figures by 1LSB if CHOP is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Integral Non Linearity                                            | •                       | ± 15                  | ppm of FSR   | 1 LSB <sub>16</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Offset Error <sup>3</sup>                                         | -2                      | _ 10                  | LSB          | Chop on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Offset Effor                                                      | See tab                 | oles                  |              | Offset error is in the order of the noise and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                   | XXXXXXXXX               |                       |              | dependent on the 16-bit calibration for the update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                   |                         |                       |              | rate chosen.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Offset Error Drift                                                | 1                       |                       | μV /°C       | Chop On                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

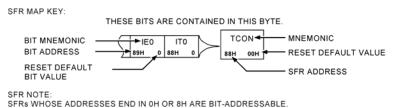

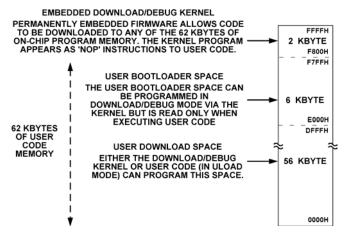

| 4                                                                 | 20                      |                       | μV /°C       | Chop Off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |