# PIC32MX

# **PIC32MX Flash Programming Specification**

### 1.0 DEVICE OVERVIEW

This document defines the programming specification for the PIC32MX family of 32-bit microcontroller devices. This programming specification is designed to guide External Programmer Tools developers. End customers developing applications for PIC32MX devices should use development tools that already provide support for device programming.

This document includes programming specifications for the PIC32MX family of devices.

## 2.0 PROGRAMMING OVERVIEW

All PIC32MX devices can be programmed via two primary methods – Self-programming and external tool programming. The self-programming method requires that the target device already contain executable code with necessary logic to complete the programming sequence. The external tool programming method, on the other hand, does not require any code in the target device – it can program all target devices with or without any executable code. This document describes the external tool programming method only. Refer to the PIC32MX Family Reference Manual (DS61132) and the PIC32MX Family Data Sheet (DS61143) to learn more about the self-programming method.

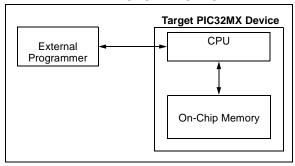

An external tool programming setup consists of an external programmer tool and a target PIC32MX device. Figure 2-1 shows the block diagram view of the typical programming setup. The programmer tool is responsible for executing necessary programming steps and completing the programming operation.

FIGURE 2-1: A PROGRAMMING SYSTEM SETUP

All PIC32MX devices provide two physical interfaces to the external programmer tool:

- 2-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- 4-wire JTAG

See Section 4.0 "Connecting to the Device" for more information.

Each of these methods may or may not use a downloadable Program Executive (PE). The PE executes from the target device RAM and hides device programming details from the programmer. It also removes overhead associated with data transfer and improves overall data throughput. Microchip has developed a PE that is available for use with any external programmer. See Section 16.0 "The Programming Executive" for more information.

**Section 3.0 "Programming Steps"** describes high level programming steps, followed by detailed discussion of each step.

See Appendices for more specific details on EJTAG, programming commands and DC specs.

### 2.1 Assumptions

Both 2 and 4-wire interfaces use the EJTAG protocol to exchange data with the programmer. While this document provides a working description of this protocol as needed, advanced users are advised to refer to the EJTAG Specification by MIPS Technology, "MD00047".

### 3.0 PROGRAMMING STEPS

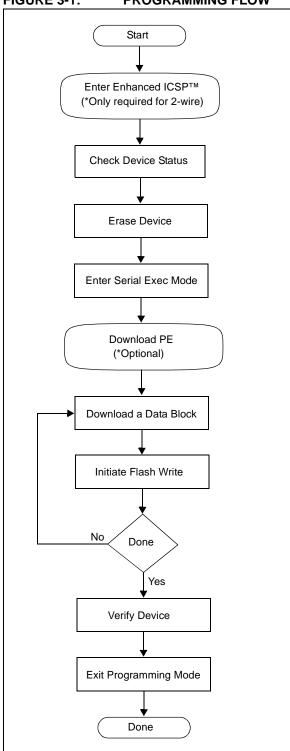

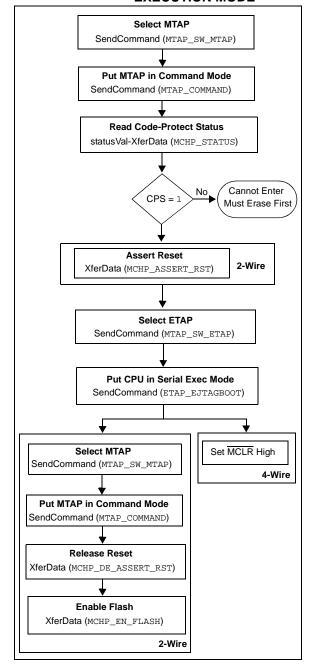

All programmers must perform a common set of steps regardless of the actual method they are using. Figure 3-1 shows the steps required to program PIC32MX devices.

FIGURE 3-1: PROGRAMMING FLOW

The following sequence lists each step and provides a brief explanation. Detailed discussion of each step is provided in following sections.

1. Connect to the target device.

To ensure successful programming, all required pins must be connected to appropriate signals. See **Section 4.0 "Connecting to the Device"** for more information.

2. Place the target device in Programming mode.

This step is not required if the 4-wire programming method is used. For 2-wire programming methods, the target device must be placed in a special Programming mode before executing further steps. See **Section 7.0** "Entering Programming Mode" for more information.

3. Check the status of the device.

This step checks the status of the device to ensure it is ready to receive information from the programmer. See **Section 8.0** "**Check Device Status**" for more information.

4. Erase the target device.

If the target memory block in the device is not blank, or the device is code-protected, an erase step must be performed before programming any new data. See **Section 9.0** "**Erasing the Device**" for more information.

5. Enter Programming mode.

This step verifies that the device is not code-protected and boots the TAP controller in order to start sending and receiving data to the PIC32MX CPU. See **10.0** "Entering Serial Execution Mode" for more information.

6. Download the Programming Executive (PE).

This step is not required if a method that does not require PE is used. The PE is a small block of executable code that is first downloaded into the RAM of the target device, which in turn receives and programs the actual data. See 11.0 "Downloading the Programming Executive (PE)" for more information.

7. Download the block of data to program.

All methods with or without PE must download the desired programming data into a block of memory in RAM. See 12.0 "Downloading a Data Block" for more information.

8. Initiate Flash Write.

After downloading each block of data into RAM, the programming sequence must be started to program it into the target device's Flash memory. See 13.0 "Initiating a Flash ROW Write" for more information.

Repeat steps 7 and 8 until all data blocks are downloaded and programmed.

### 10. Verify the program memory.

After all programming data and Configuration bits are programmed, the target device memory should be read back and verified for the matching content. See **14.0** "Verify Device Memory" for more information.

### 11. Exit the Programming mode.

The newly programmed data is not effective until either power is removed and reapplied to the target device or an exit programming sequence is performed. See **15.0** "Exiting Programming Mode" for more information.

### 4.0 CONNECTING TO THE DEVICE

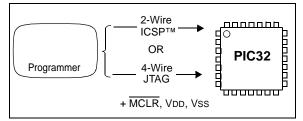

The PIC32MX family provides two possible physical interfaces for connecting to and programming the memory contents (Figure 4-1). For all programming interfaces, the target device must be properly powered and all required signals must be connected.

FIGURE 4-1: PROGRAMMING INTERFACES

### 4.1 4-Wire Interface

One possible interface is the 4-wire JTAG (IEEE 1149.1) port. Table 4-1 lists the required pin connections. This interface uses the following 4 communication lines to transfer data to and from the PIC32MX device being programmed:

- TCK Test Clock Input

- TMS Test Mode Select Input

- TDI Test Data Input

- TDO Test Data Output

These signals are described in detail below. Refer to the data sheet of the particular device for the connection of the signals to chip pins.

### 4.1.1 TEST CLOCK INPUT (TCK)

TCK is the clock that controls the updating of the TAP controller and the shifting of data through the instruction or selected data register(s). TCK is independent of the processor clock with respect to both frequency and phase.

### 4.1.2 TEST MODE SELECT INPUT (TMS)

TMS is the control signal for the TAP controller. This signal is sampled on the rising edge of TCK.

### 4.1.3 TEST DATA INPUT (TDI)

TDI is the test data input to the instruction or selected data register(s). This signal is sampled on the rising edge of TCK for some TAP controller states.

### 4.1.4 TEST DATA OUTPUT (TDO)

TDO is the test data output from the instruction or data register(s). This signal changes on the falling edge of TCK. TDO is only driven when data is shifted out, otherwise the TDO is tri-stated.

TABLE 4-1: 4-WIRE INTERFACE PINS

| Din Name                    |          |          |                                      |

|-----------------------------|----------|----------|--------------------------------------|

| Pin Name                    | Pin Name | Pin Type | Pin Description                      |

| MCLR                        | MCLR     | Р        | Programming Enable                   |

| ENVREG                      | ENVREG   | I        | Enable for On-Chip Voltage Regulator |

| VDD and AVDD(1)             | VDD      | Р        | Power Supply                         |

| Vss and AVss <sup>(1)</sup> | Vss      | Р        | Ground                               |

| VDDCORE                     | VDDCORE  | Р        | Regulated Power Supply for Core      |

| TDI                         | TDI      | I        | Test Data In                         |

| TDO                         | TDO      | 0        | Test Data Out                        |

| TCK                         | TCK      | I        | Test Clock                           |

| TMS                         | TMS      | I        | Test Mode State                      |

**Legend:** I = Input, O = Output, P = Power

**Note 1:** All power supply and ground pins must be connected, including analog supplies (AVDD) and ground (AVss).

### 4.2 2-Wire Interface

Another possible interface is the 2-wire ICSP port. Table 4-2 lists the required pin connections. This interface uses the following 2 communication lines to transfer data to and from the PIC32MX device being programmed:

- PGCx Serial Program Clock

- PGDx Serial Program Data

These signals are described in detail below. Refer to the data sheet of the particular device for the connection of the signals to chip pins.

### 4.2.1 SERIAL PROGRAM CLOCK (PGCx)

PGCx is the clock that controls the updating of the TAP controller and the shifting of data through the instruction or selected data register(s). PGCx is independent of the processor clock, with respect to both frequency and phase.

### 4.2.2 SERIAL PROGRAM DATA (PGDx)

PGDx is the data input/output to the instruction or selected data register(s), it is also the control signal for the TAP controller. This signal is sampled on the falling edge of PGC for some TAP controller states.

TABLE 4-2: 2-WIRE INTERFACE PINS

| Pin Name                    |          |          |                                              |

|-----------------------------|----------|----------|----------------------------------------------|

| Pin Name                    | Pin Name | Pin Type | Pin Description                              |

| MCLR                        | MCLR     | Р        | Programming Enable                           |

| ENVREG                      | ENVREG   | I        | Enable for On-Chip Voltage Regulator         |

| VDD and AVDD(1)             | VDD      | Р        | Power Supply                                 |

| Vss and AVss <sup>(1)</sup> | Vss      | Р        | Ground                                       |

| VDDCORE                     | VDDCORE  | Р        | Regulated Power Supply for Core              |

| PGC1                        | PGC      | I        | Primary Programming Pin Pair: Serial Clock   |

| PGD1                        | PGD      | I/O      | Primary Programming Pin Pair: Serial Data    |

| PGC2                        | PGC      | I        | Secondary Programming Pin Pair: Serial Clock |

| PGD2                        | PGD      | I/O      | Secondary Programming Pin Pair: Serial Data  |

**Legend:** I = Input, O = Output, P = Power

**Note 1:** All power supply and ground pins must be connected, including analog supplies (AVDD) and ground (AVss).

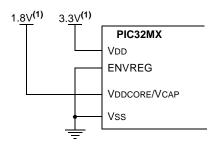

### 4.3 Power Requirements

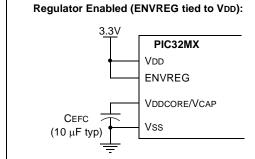

All devices in the PIC32MX family are dual voltage supply designs: one supply for the core and peripherals and another for the I/O pins. Some devices contain an on-chip regulator to alleviate the need for two external voltage supplies.

All of the PIC32MX devices power their core digital logic at a nominal 1.8V. This may create an issue for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the PIC32MX family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. A low ESR capacitor (such as tantalum) must be connected to the VDDCORE pin (Figure 4-2). This helps to maintain the stability of the regulator. The specifications for core voltage and capacitance are listed in Section 20.0 "Appendix C: AC/DC Characteristics and Timing Requirements".

FIGURE 4-2: CONNECTIONS FOR THE ON-CHIP REGULATOR

### Regulator Disabled (ENVREG tied to ground):

Note 1: These are typical operating voltages. Refer to Section 20.0 "Appendix C: AC/DC Characteristics and Timing Requirements" for the full operating ranges of VDD and VDDCORE.

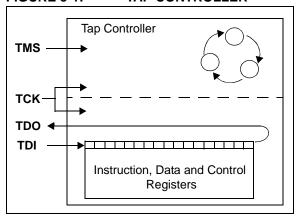

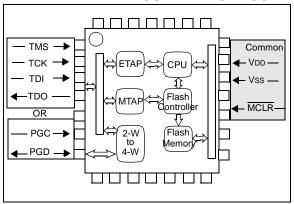

### 5.0 EJTAG vs. ICSP

Programming is accomplished via the EJTAG module in the CPU core. EJTAG is connected to either the full set of JTAG pins, or a reduced 2-wire to 4-wire EJTAG interface. In both modes, programming of the PIC32MX Flash memory is accomplished through the ETAP controller. The TAP Controller uses the TMS pin to determine if instruction or data registers should be accessed in the shift path between TDI and TDO (see Figure 5-1).

FIGURE 5-1: TAP CONTROLLER

The basic concept of EJTAG that is used for programming is the use of a special memory area called DMSEG (FF200000h-FF2FFFFFh), which is only available when the processor is running in DEBUG mode. All instructions are serially shifted into an internal buffer, then loaded into the instruction register and executed by the CPU. Instructions are fed through the ETAP State machine 32 bits at a time.

FIGURE 5-2: BASIC PIC32MX

PROGRAMMING BLOCK

#### 2-Wire to 4-Wire:

Converts 2-wire ICSP interface to 4-wire JTAG.

### • ETAP

Serially feeds instructions and data into CPU.

#### MTAP

- In addition to the EJTAG TAP (ETAP) controller, the PIC32MX device uses a second proprietary TAP controller for additional operations. The Microchip TAP (MTAP) controller supports two instructions relevant to programming. These are the MTAP\_COMMAND and MTAP\_SWTAP instructions, see Table 19-1 for a complete list of commands. The MTAP\_COMMAND instruction provides a mechanism for a JTAG probe to send commands to the device via its data register.

- The programmer sends commands by shifting in the MTAP\_COMMAND instruction via the SendCommand pseudo op, and then sending MTAP\_COMMAND DR commands via XferData psuedo op (see Table 19-2 for specific commands). The probe does not need to issue an MTAP\_COMMAND instruction for every command shifted into the data register.

#### • CPU

- The CPU executes instructions at 8 MHz via the internal oscillator.

#### Flash Controller

The Flash Controller controls erasing and programming of the Flash memory on the device.

### Flash Memory

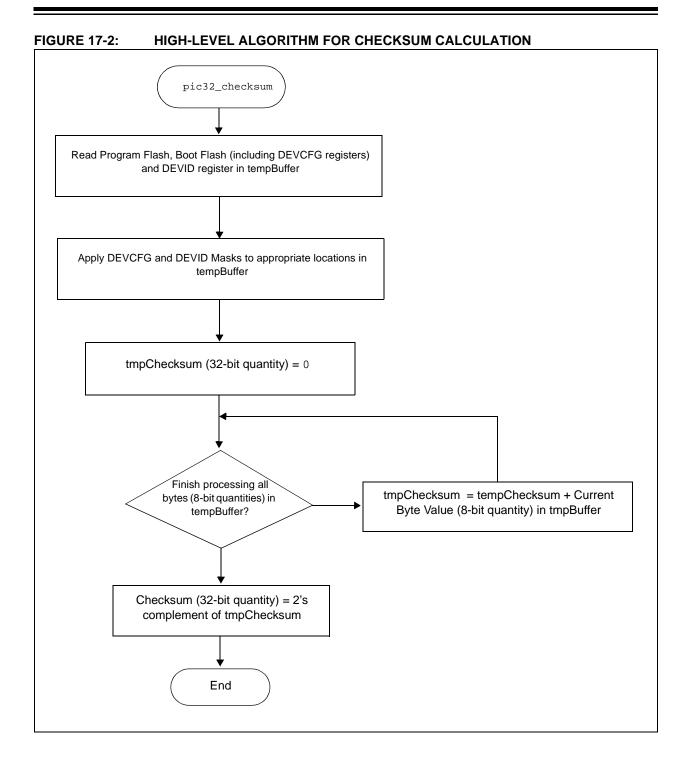

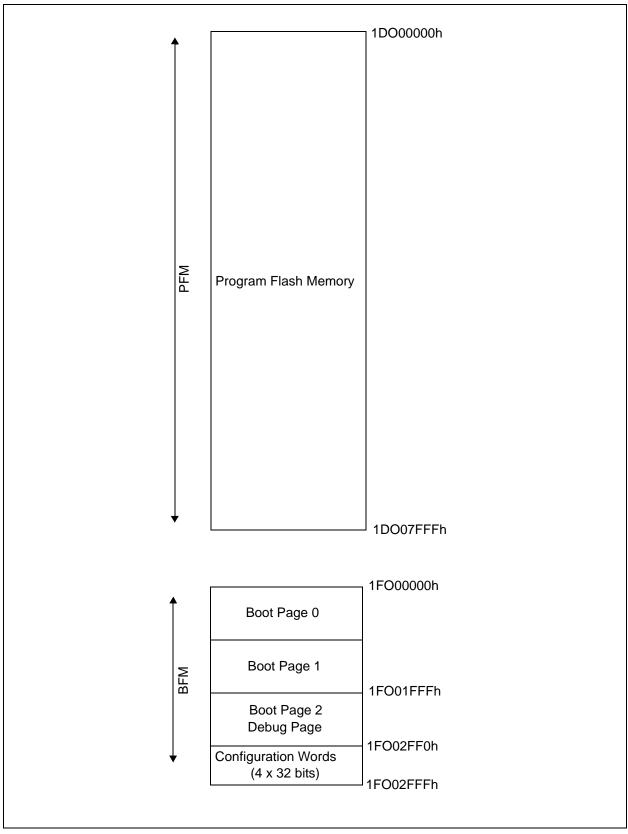

- The PIC32MX device Flash memory is divided into two logical Flash partitions consisting of the Boot Flash Memory (BFM) and Program Flash Memory (PFM). The Boot Flash Memory (BFM) map extends from 1FC00000h to 1FC02FFFh, and the Program Flash Memory (PFM) map extends from 1D000000h to 1D07FFFh. Code storage begins with the BFM and supports up to 12K bytes, then continues with the PFM which supports up to 512K bytes. Table 5-1 shows the program memory size of each device variant. Each erase block, or page, contains 1K instructions (4 KBytes), and each program block, or row, contains 128 instructions (512 Bytes).

- The last four implemented program memory locations in BFM are reserved for the Device Configuration registers.

TABLE 5-1: CODE MEMORY SIZE

| PIC32MX Device  | Boot Flash Memory Address (Bytes) | Program Flash Memory Address<br>(Bytes) |

|-----------------|-----------------------------------|-----------------------------------------|

| PIC32MX300F032H | 1FC00000h-1FC02FFFh (12KB)        | 1D000000h-1D007FFFh (32KB)              |

| PIC32MX320F064H | 1FC00000h-1FC02FFFh (12KB)        | 1D000000h-1D00FFFFh (64KB)              |

| PIC32MX320F128H | 1FC00000h-1FC02FFFh (12KB)        | 1D000000h-1D01FFFFh (128KB)             |

| PIC32MX340F256H | 1FC00000h-1FC02FFFh (12KB)        | 1D000000h-1D03FFFFh (256KB)             |

| PIC32MX320F128L | 1FC00000h-1FC02FFFh (12KB)        | 1D000000h-1D01FFFFh (128KB)             |

| PIC32MX360F256L | 1FC00000h-1FC02FFFh(12KB)         | 1D000000h-1D03FFFFh(256KB)              |

| PIC32MX360F512L | 1FC00000h-1FC02FFFh(12KB)         | 1D000000h-1D07FFFFh(512KB)              |

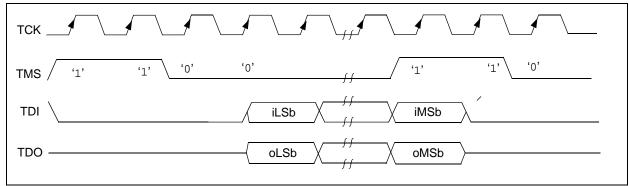

### 5.1 4-Wire JTAG Details

The 4-wire interface uses standard JTAG (IEEE 1149.1) interface signals.

- TCK: Test Clock drives data in/out

- TMS: Test Mode Select Selects operational mode

- TDI: Test Data In Data into the device

- TDO: Test Data Out Data out of the device

Since only one data line is available, the protocol is necessarily serial, like SPI. The clock input is at the TCK pin. Configuration is performed by manipulating a state machine one bit at a time through the TMS pin. One bit of data is transferred in and out per TCK clock pulse at the TDI and TDO pins, respectively. Different instruction modes can be loaded to read the chip ID or manipulate chip functions.

Data presented to TDI must be valid for a chip specific setup time before, and hold time after the rising edge of TCK. TDO data is valid for a chip specific time after the falling edge of TCK. Refer to Figure 5-3.

### 5.2 2-wire ICSP Details

When in this mode the 2-wire ICSP signals are time multiplexed into the 2-wire to 4-wire block. The 2-wire to 4-wire block then converts the signals to look like a 4-wire JTAG port to the TAP controller.

There are two possible modes of operation:

- 4-Phase ICSP

- 2-Phase ICSP

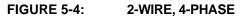

### 5.2.1 4-PHASE ICSP

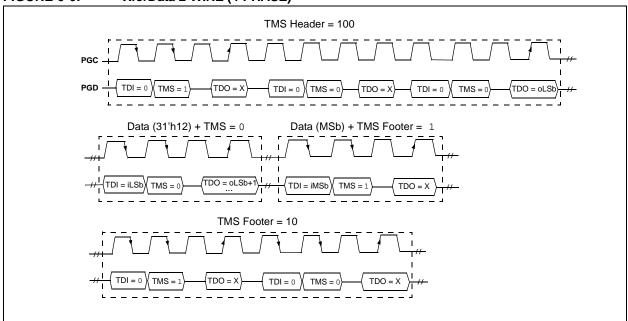

In 4-Phase ICSP, TDI, TDO, and TMS are multiplexed onto PGD in 4 clocks (see Figure 5-4). The Least Significant bit (LSb) is shifted first, and TDI and TMS are sampled on the falling edge of PGC while TDO is driven on the falling edge of PGC. 4-Phase mode is used for both read and write data transfers.

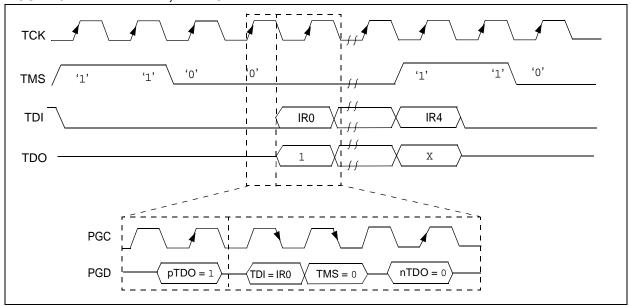

### 5.2.2 2-PHASE ICSP

In 2-Phase ICS, TMS and TDI are multiplexed into PGD in 2 clocks (see Figure 5-5). The LSb is shifted first, and TDI and TMS are sampled on the falling edge of PGC. There is no TDO output provided in this mode. This mode was designed to accelerate 2-Wire, write-only transactions.

**Note:** The packet is NOT actually executed until the first clock of the next packet.

### 6.0 PSEUDO OPERATIONS

To simplify the description of programming details, all operations will be described using pseudo operations. There are several functions used in the pseudocode descriptions. These are used either to make the pseudocode more readable, to abstract implementation-specific behavior, or both. When passing parameters with pseudo operation, the following syntax will be used: 5'h0x03 (i.e.,send 5 bit hex value 0x03). These functions are defined in this section, and include the following:

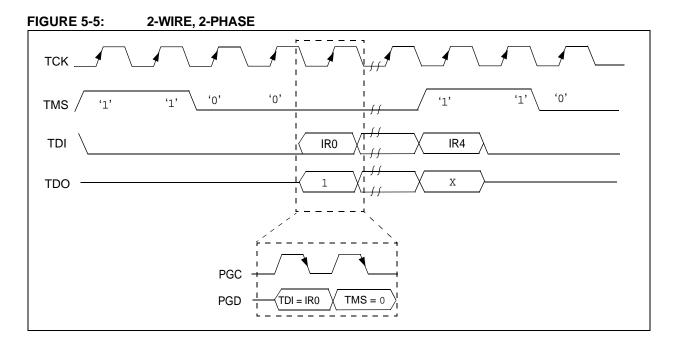

- SetMode (mode)

- SendCommand (command)

- oData = XferData (iData)

- oData = XferFastData (iData)

- oData = **XferInstruction** (instruction)

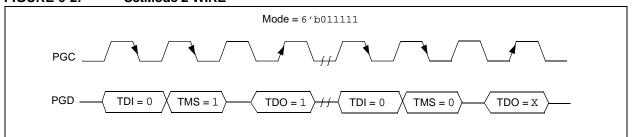

## 6.1 SetMode Pseudo Operation

Format: SetMode (mode)

Purpose:

To set the EJTAG state machine to a specific state.

### **Description:**

The value of mode is clocked into the device on signal TMS. TDI is set to a '0' and TDO is ignored.

#### Restrictions:

None.

### Example:

**SetMode**(6'b011111)

### FIGURE 6-1: SetMode 4-WIRE

### FIGURE 6-2: SetMode 2-WIRE

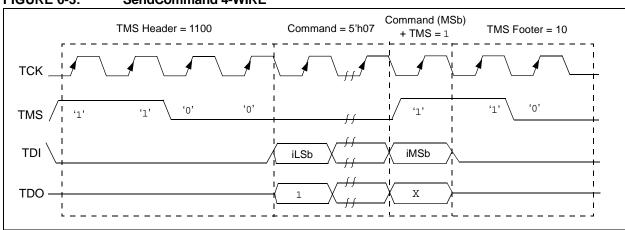

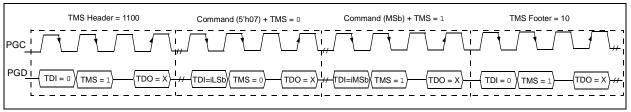

# 6.2 SendCommand Pseudo Operation

Format: SendCommand (command)

Purpose:

To send a command to select a specific TAP register.

### **Description:**

First the TMS Header is clocked into the device to select the Shift IR state. The command is then clocked into the device on TDI while holding signal TMS low. The last Most Significant bit (MSb) of the command is then clocked in while setting TMS high. Finally, the TMS Footer is clocked in on TMS to return the TAP controller to the Run/Test Idle state.

Restrictions:

None.

Example:

SendCommand (5'h07)

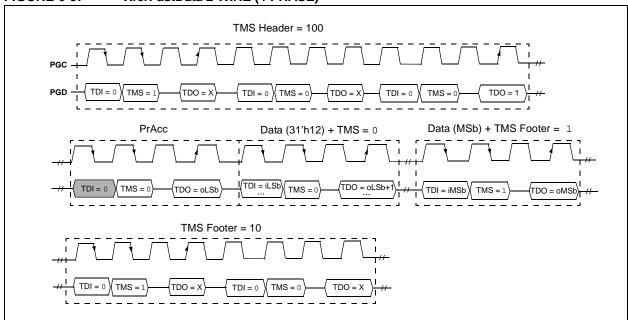

FIGURE 6-3: SendCommand 4-WIRE

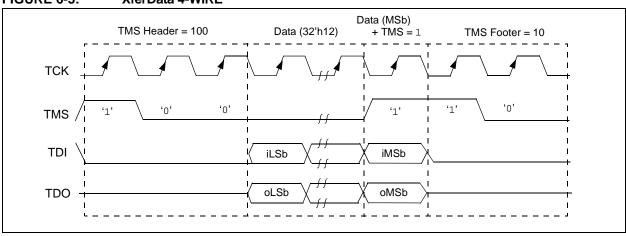

## 6.3 XferData Pseudo Operation

Format: oData = XferData (iData)

Purpose:

To clock data to and from the register selected by the command.

### **Description:**

First the TMS Header is clocked into the device to select the Shift DR state. The data is then clocked in/out of the device on TDI/TDO while holding signal TMS low. The last MSb of the data is then clocked in/out while setting TMS high. Finally, the TMS Footer is clocked in on TMS to return the TAP controller to the Run/Test Idle state.

Restrictions:

None.

### Example:

oData = XferData (32'h12)

FIGURE 6-5: XferData 4-WIRE

FIGURE 6-6: XferData 2-WIRE (4-PHASE)

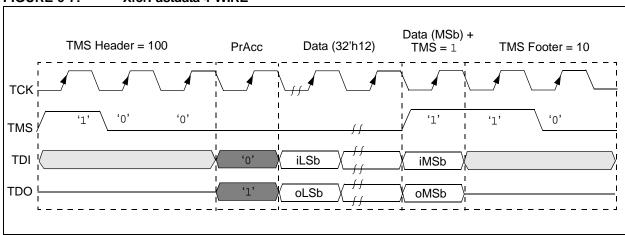

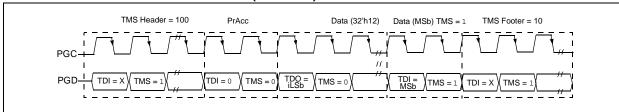

## 6.4 XferFastData Pseudo Operation

Format: oData = XferFastData (iData)

Purpose:

To send 32 bits of data in/out of the device fast.

### **Description:**

First the TMS Header is clocked into the device to select the Shift DR state. For 2-wire (4-phase), note that on the last clock, oPrAcc bit is shifted out on TDO while clocking in the TMS Header. If the value of oPrAcc is not '1', then the whole operation must be repeated. Next, the input value of PrAcc bit, which is '0', is clocked in. For 2-wire (4-phase), the TDO during this operation will be the LSb of out output. The rest of the 31 bits of the input data is clocked in and the 31 bits of output data is clocked out. For the last bit of the input data, the TMS Footer = 1 is set. Finally, TMS Footer = 10 is clocked in to return the TAP controller to the Run/Test Idle state.

#### Restrictions:

The SendCommand (ETAP\_FASTDATA) must be sent first to select the Fastdata register. See Table 19-4 for complete description of commands.

The 2-Phase XferData is only used when talking to the PE. See **Section 16.0** "The **Programming Executive**" for more details.

### Example:

// Select the Fast Data Register

SendCommand(ETAP\_FASTDATA)

// Send/Receive 32-bit Data

oData = XferFastData(32'h12)

FIGURE 6-7: XferFastdata 4-WIRE

### FIGURE 6-8: XferFastdata 2-WIRE (2-PHASE)

## 6.5 XferInstruction Pseudo Operation

Format: XferInstruction (instruction)

Purpose:

To send 32 bits of data for the device to execute.

**Description:**

The instruction is clocked into the device and then executed by CPU.

**Restrictions:**

The device must be in Debug mode.

### **EXAMPLE 6-1: XferInstruction EXAMPLE**

```

XferInstruction (instruction)

{

// Select Control Register

SendCommand(ETAP_CONTROL);

// Wait until CPU is ready

// Check if Processor Access bit (bit 18) is set

do {

controlVal = XferData(32'h0x0004C000);

} while( PrAcc(contorlVal<18>) is not '1' );

// Select Data Register

SendCommand(ETAP_DATA);

// Send the instruction

XferData(instruction);

// Tell CPU to execute instruction

SendCommand(ETAP_CONTROL);

XferData(32'h0x0000C000);

}

```

# 7.0 ENTERING PROGRAMMING MODE

This step is not required if a 4-wire programming method is used. For 2-wire programming methods, the target device must be placed in a special Programming mode before executing further steps.

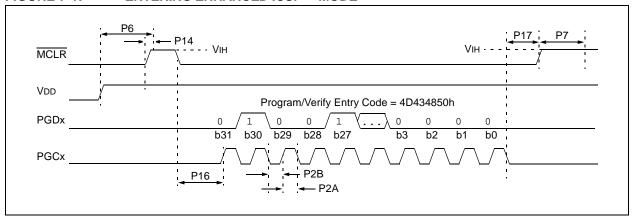

The following steps are required to enter Programming mode:

- 1. The MCLR pin is briefly driven high, then low.

- 2. A 32-bit key sequence is clocked into PGDx.

- 3. Finally, MCLR is then driven high within a specified period of time and held.

Please refer to 20.0 "Appendix C: AC/DC Characteristics and Timing Requirements" for timing requirements.

The programming voltage applied to MCLR is VIH, which is essentially VDD in the case of PIC32MX devices. There is no minimum time requirement for

holding at VIH. After VIH is removed, an interval of at least P16 must elapse before presenting the key sequence on PGDx.

The key sequence is a specific 32-bit pattern: '0100 1101 0100 0011 0100 1000 0101 0000' (more easily remembered as ascii 'MCHP'). The device will enter Program/Verify mode only if the key sequence is valid. The Most Significant bit (MSb) of the Most Significant nibble must be shifted in first.

Once the key sequence is complete, VIH must be applied to MCLR and held at that level for as long as Programming mode is to be maintained. An interval of at least time P17 and P7 must elapse before presenting data on PGDx. Signals appearing on PGDx before P7 has elapsed will not be interpreted as valid.

Upon successful entry, the program memory can be accessed and programmed in serial fashion. While in the Programming mode, all unused I/Os are placed in the high-impedance state.

FIGURE 7-1: ENTERING ENHANCED ICSP™ MODE

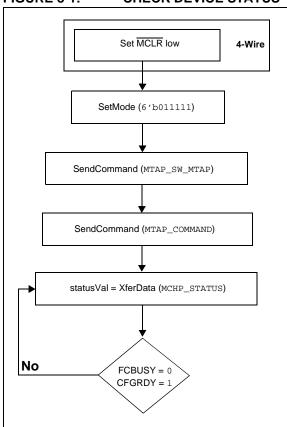

### 8.0 CHECK DEVICE STATUS

Before a device can be programmed, the programmer must check the status of the device to ensure it is ready to receive information.

FIGURE 8-1: CHECK DEVICE STATUS

### 8.1 4-Wire Interface

Four-wire JTAG programming is a Mission mode operation and therefore the setup sequence to begin programing should be done while asserting MCLR. Holding the device in Reset prevents the processor from executing instructions or driving ports.

The following steps are required to check the device status using the 4-wire interface:

- 1. Set MCLR pin low.

- SetMode (6'b011111) to force the Chip TAP controller into RUN TEST/IDLE state.

- 3. SendCommand (MTAP\_SW\_MTAP)

- 4. SendCommand (MTAP\_COMMAND)

- 5. statusVal = XferData (MCHP\_STATUS).

- 6. If CFGRDY (statusVal<3>) is not '1' and FCBUSY (statusVal<2>) is not '0' GOTO step 5.

### 8.2 2-Wire Interface

The following steps are required to check the device status using the 2-wire interface:

- SetMode (6'b011111) to force the Chip TAP controller into RUN TEST/IDLE state.

- 2. SendCommand (MTAP\_SW\_MTAP)

- 3. SendCommand (MTAP\_COMMAND)

- 4. statusVal = XferData (MCHP\_STATUS).

- 5. If CFGRDY (statusVal<3>) is not '1' and FCBUSY (statusVal<2>) is not '0' GOTO step 4.

**Note:** If CFGRDY and FCBUSY do not come to the proper state within 10 ms, the sequence may have been executed wrong or the device is damaged.

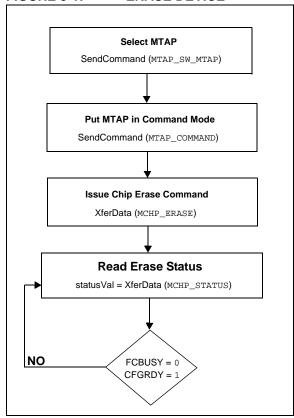

### 9.0 ERASING THE DEVICE

Before a device can be programmed, it must be erased. The erase operation writes all '1's to the Flash memory and prepares it to program a new set of data. Once a device is erased, it can be verified by performing a "Blank Check" operation. See **Section 9.1** "**Blank Check**" for more information.

The procedure for erasing program memory (Program, Boot, and Configuration memory) consists of selecting the MTAP and sending the MCHP\_ERASE command. The programmer then must wait for the erase operation to complete by reading and verifying bits in the MCHP\_STATUS value. Figure 9-1 shows the process for performing a Chip Erase.

**Note:** The Device ID memory locations are read-only and can not be erased. Thus, Chip Erase has no effect on these memory locations.

FIGURE 9-1: ERASE DEVICE

The following steps are required to erase a target device:

- 1. SendCommand (MTAP\_SW\_MTAP).

- 2. SendCommand (MTAP\_COMMAND).

- 3. XferData (MCHP\_ERASE).

- 4. statusVal = XferData (MCHP\_STATUS).

- 5. If CFGRDY (statusVal<3>) is not '1' and FCBUSY (statusVal<4>) is not '0' GOTO to step 4.

**Note:** The Chip Erase operation is a self-timed operation. If the FCBUSY and CFGRDY bits do not become properly set within the specified Chip Erase time, the sequence may have been executed wrong or the device is damaged.

### 9.1 Blank Check

The term "Blank Check" implies verifying that the device has been successfully erased and has no programmed memory locations. A blank or erased memory location is always read as '1'.

The device Configuration registers are ignored by the Blank Check. Additionally, all unimplemented memory space should be ignored from the Blank Check.

DS61145D-page 18

# 10.0 ENTERING SERIAL EXECUTION MODE

Before a device can be programmed, it must be placed in Serial Execution mode.

The procedure for entering Serial Execution mode consists of verifying the device is not code-protected, if the device is code-protected a Chip Erase must be performed. See **Section 9.0** "**Erasing the Device**" for details.

FIGURE 10-1: ENTERING SERIAL EXECUTION MODE

### 10.1 4-Wire Interface

The following steps are required to enter Serial Execution mode:

- 1. SendCommand (MTAP\_SW\_MTAP).

- 2. SendCommand (MTAP\_COMMAND).

- 3. statusVal = XferData (MCHP\_STATUS).

- 4. If CPS (statusVal<7>) is not '1' the device must be erased first.

- 5. SendCommand (MTAP\_SW\_ETAP).

- 6. SendCommand (ETAP\_EJTAGBOOT).

- 7. Set MCLR 'High'.

### 10.2 2-wire Interface

The following steps are required to enter Serial Execution mode:

- 1. SendCommand (MTAP\_SW\_MTAP).

- 2. SendCommand (MTAP\_COMMAND).

- statusVal = XferData (MCHP\_STATUS).

- If CPS (statusVal<7>) is not '1' the device must be erased first.

- 5. XferData (MCHP\_ASSERT\_RST).

- 6. SendCommand (MTAP\_SW\_ETAP).

- 7. SendCommand (ETAP\_EJTAGBOOT).

- 8. SendCommand (MTAP\_SW\_MTAP).

- 9. SendCommand (MTAP\_COMMAND).

- 10. XferData (MCHP\_DE\_ASSERT\_RST).

- 11. XferData (MCHP\_EN\_FLASH).

### 11.0 DOWNLOADING THE PROGRAMMING EXECUTIVE (PE)

The programming executive resides in RAM memory and is executed by CPU to program the device. The programming executive provides the mechanism for the programmer to program and verify PIC32MX devices using a simple command set and communication protocol. There are several basic functions provided by the programming executive:

- Read Memory

- Erase Memory

- · Program Memory

- · Blank Check

- Read Executive Firmware Revision

- · Get CRC of Flash Memory Locations

The programming executive performs the low-level tasks required for programming and verifying a device. This allows the programmer to program the device by issuing the appropriate commands and data. A detailed description for each command is provided in Section 16.2 "Programming Executive Command Set".

The programming executive uses the device's data RAM for variable storage and program execution. After the programming executive has run, no assumptions should be made about the contents of data RAM.

After the programming executive is loaded into the data RAM, the PIC32MX family can be programmed using the command set shown in Table 16-1.

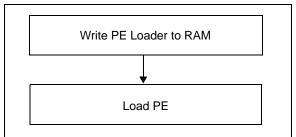

**FIGURE 11-1: DOWNLOAD PE**

Loading the programming executive in the memory is a two step process:

- 1. Load the PE loader in the data RAM. (The PE loader loads the programming executive binary file in the proper location of the data RAM, and when done, jumps to the programming exec and starts executing it.)

- 2. Feed the programming executive binary to the PE loader.

The following steps are required to download the programming executive:

**TABLE 11-1: DOWNLOAD PROGRAM EXEC**

| Operation                                              |             | Operand                             |  |

|--------------------------------------------------------|-------------|-------------------------------------|--|

| Step 1: Initialize BMXCON to 0x1f0040. The instruction |             |                                     |  |

| sequence executed by the PIC32MX core is as follows:   |             |                                     |  |

| lui                                                    | a0,0xbf88   |                                     |  |

| ori                                                    | a0,a0,0x200 | 0 /* address of BMXCON */           |  |

| lui                                                    | a1,0x1f     |                                     |  |

| ori                                                    | a1,a1,0x40  | /* \$a1 has 0x1f0040 */             |  |

| sw                                                     | a1,0(a0)    | <pre>/* BMXCON initialized */</pre> |  |

| XferInstruction                                        |             | 0x3c04bf88                          |  |

| XferInstruction                                        |             | 0x34842000                          |  |

| XferInstruction                                        |             | 0x3c05001f                          |  |

| XferInstruction                                        |             | 0x34a50040                          |  |

| XferInstruction                                        |             | 0xac850000                          |  |

|                                                        |             |                                     |  |

Step 2: Initialize BMXDKPBA to 0x800. The instruction sequence executed by the PIC32MX core is as follows:

| Xferl | nstruction | 0x34050800 |

|-------|------------|------------|

| sw    | a1,16(a0)  |            |

| li    | a1,0x800   |            |

| 7(101111011101110111                                | 0.0000000  |

|-----------------------------------------------------|------------|

| XferInstruction                                     | 0xac850010 |

| Step 3: Initialize BMXDUDBA and BMXDUPBA to 0x8000. |            |

The instruction sequence executed by the PIC32MX core is as follows:

```

li

a1,0x8000

SW

a1,32(a0)

a1,48(a0)

SW

```

| , , ,           |            |

|-----------------|------------|

| XferInstruction | 0x34058000 |

| XferInstruction | 0xac850020 |

| XferInstruction | 0xac850030 |

Step 4: Setup PIC32MX RAM address for PE. The instruction sequence executed by the PIC32MX core is as follows:

lui a0,0xa000 an an ny8nn

| 011 a0,a0,0x800 |            |

|-----------------|------------|

| XferInstruction | 0x3c04a000 |

| XferInstruction | 0x34840800 |

Step 5: Load PE\_Loader. Repeat this step (step 5) until the entire PE\_Loader is loaded in the PIC32MX memory. In the operands field, "<PE\_loader hi++>" represents the MSbs 31-to-16 of the PE loader opcodes shown in Table 11.2. Likewise, "<PE\_loader lo++>" represents the LSbs 15-to-0 of the PE loader opcodes shown in Table 11.2. The "++" sign indicates that when these operations are performed in succession, the new word is to be transferred from the list of opcodes of the LPE Loader shown in Table 11.2. The instruction sequence executed by the PIC32MX core is as follows:

lui a2, <PE\_loader hi++> ori a0,a0, <PE\_loader lo++> SW a2,0(a0)

addiu a0,a0,4

TABLE 11-1: DOWNLOAD PROGRAM EXEC (CONTINUED)

| XferInstruction | (0x3c06 <pe_loader hi++="">)</pe_loader> |

|-----------------|------------------------------------------|

| XferInstruction | (0x34c6 <pe_loader lo++="">)</pe_loader> |

| XferInstruction | 0xac860000                               |

| XferInstruction | 0x24840004                               |

**Step 6:** Jump to PE\_Loader. The instruction sequence executed by the PIC32MX core is as follows:

lui t9,0xa000

ori t9,t9,0x800

jr t9

nop

| XferInstruc | ction | 0x3c19a000 |

|-------------|-------|------------|

| XferInstruc | ction | 0x37390800 |

| XferInstruc | ction | 0x03200008 |

| XferInstruc | ction | 0x00000000 |

**Step 7:** Load PE using the PE\_Loader. Repeat this step (step 7) until the entire PE is loaded in the PIC32MX memory. In this step, you are given a Intel(R) Hex format file of Program Executive that you will parse and transfer number of 32-bit words at a time to the PIC32MX memory. The instruction sequence executed by the PIC32MX is shown in the "Instruction" column of Table 11.2, PE Loader Opcodes.

| SendCommand  | ETAP_FASTDATA                                                                |

|--------------|------------------------------------------------------------------------------|

| XferFastData | PE_ADDRESS (Address of PE program block from PE Hex file)                    |

| XferFastData | PE_SIZE (Number of 32-bit<br>words of the program block<br>from PE Hex file) |

| XferFastData | PE software opcode from PE<br>Hex file (PE Instructions)                     |

|              |                                                                              |

**Step 8:** Jump to PE. Magic number (0xDEAD0000) instructs the PE\_Loader that PE is completely loaded in the memory. When the PE\_Loader sees the magic number, it jumps to PE.

|              | loaded in the memory. When the PE_Loader sees |            |  |

|--------------|-----------------------------------------------|------------|--|

|              | the magic number, it jumps to PE.             |            |  |

| XferFastData |                                               | 0x00000000 |  |

|              | XferFastData                                  | 0xDFAD0000 |  |

TABLE 11-2: PE LOADER OPCODES

| Opcode     | Instruction                 |

|------------|-----------------------------|

| 0x3c07dead | lui a3, 0xdead              |

| 0x3c06ff20 | lui a2, 0xff20              |

| 0x3c05ff20 | lui al, 0xff20              |

|            | herel:                      |

| 0x8cc40000 | lw a0, 0 (a2)               |

| 0x8cc30000 | lw v1, 0 (a2)               |

| 0x1067000b | beq v1, a3, <here3></here3> |

| 0x0000000  | nop                         |

| 0x1060fffb | beqz v1, <here1></here1>    |

| 0x0000000  | nop                         |

|            | here2:                      |

| 0x8ca20000 | lw v0, 0 (a1)               |

| 0x2463ffff | addiu v1, v1, -1            |

| 0xac820000 | sw v0, 0 (a0)               |

| 0x2484004  | addiu a0, a0, 4             |

| 0x1460fffb | bnez v1, <here2></here2>    |

| 0x0000000  | nop                         |

| 0x1000fff3 | b <here1></here1>           |

| 0x0000000  | nop                         |

|            | here3:                      |

| 0x3c02a000 | lui v0, 0xa000              |

| 0x34420900 | ori v0, v0, 0x900           |

| 0x00400008 | jr v0                       |

| 0x00000000 | nop                         |

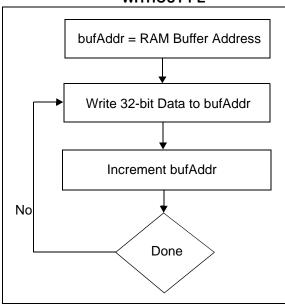

# 12.0 DOWNLOADING A DATA BLOCK

To program a block of data to the PIC32MX device, it must first be loaded into SRAM.

### 12.1 Without PE

To program a block of memory without the use of the PE, the block of data must first be written to RAM. This method requires the programmer to transfer the actual machine instructions with embedded data for writing the block of data to the devices internal RAM memory.

FIGURE 12-1: DOWNLOADING DATA WITHOUT PE

The following steps are required to download a block data:

- XferInstruction (opcode).

- Repeat step 1 until last instruction is transferred to CPU.

TABLE 12-1: DOWNLOAD DATA OPCODES

| Opcode                                                             | Instruction                                                                                                                                        |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Step 1: Initialize S<br>0xA000_0000                                | SRAM Base Address to                                                                                                                               |

| 3c10a000                                                           | lui \$s0, 0xA000;                                                                                                                                  |

| Step 2: Write the programmed into                                  | entire row of data to be system SRAM.                                                                                                              |

| 3c08 <data><br/>3508<data><br/>ae08<offset></offset></data></data> | <pre>lui \$t0, <data(31:16)>; ori \$t0, <data(15:0)>; sw \$t0, <offset>(\$s0); // OFFSET increments by 4</offset></data(15:0)></data(31:16)></pre> |

| Step3: Repeat Step 2 until 1 row of data has been loaded.          |                                                                                                                                                    |

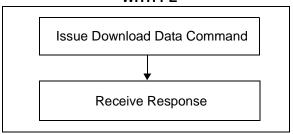

### 12.2 With PE

When using the PE, the code memory is programmed with the Program command (see Table 16-3). The program can program up to one row of code memory starting from the memory address specified in the command. The number of Program commands required to program a device depends on the number of write blocks that must be programmed in the device.

FIGURE 12-2: DOWNLOADING DATA WITH PE

The following steps are required to download a block of data using the PE:

- 1. XferFastData (PROGRAM|DATA\_SIZE).

- 2. XferFastData (ADDRESS).

- 3. response = XferFastData (32'h0x00)

# 13.0 INITIATING A FLASH ROW WRITE

Once a row of data has been downloaded into the devices SRAM, the programming sequence must be initiated to write the block of data to Flash memory.

### 13.1 Without PE

Flash memory write operations are controlled by the NVMCON register. Programming is performed by setting NVMCON to select the type of write operation and initiating the programming sequence by setting the NVMWR control bit NVMCON<15>.

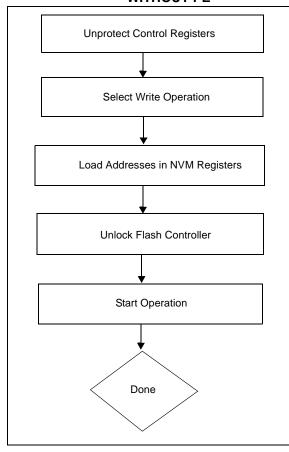

FIGURE 13-1: INITIATING FLASH WRITE WITHOUT PE

The following steps are required to initiate a Flash write:

- 1. XferInstruction (opcode).

- Repeat step 1 until the last instruction is transferred to CPU.

TABLE 13-1: INITIATE FLASH ROW WRITE OPCODES

| Opcode             | Instruct  | ion           |

|--------------------|-----------|---------------|

| Step 1: Initialize | some cons | stants.       |

| 3c04bf80           | lui       | a0,0xbf80     |

| 3484f400           | ori       | a0,a0,0xf400  |

| 34054003           | ori       | a1,\$0,0x4003 |

| 34068000           | ori       | a2,\$0,0x8000 |

| 34074000           | ori       | a3,\$0,0x4000 |

| 3c11aa99           | lui       | s1,0xaa99     |

| 34116655           | ori       | s1,\$0,0x6655 |

| 3c125566           | lui       | s2,0x5566     |

| 341299aa           | ori       | s2,\$0,0x99aa |

| 3c13ff20           | lui       | s3,0xff20     |

| 3c10a000           | lui       | s0,0xa000     |

**Step 2:** Set NVMADDR with the address of the Flash row to be programmed.

| 3c08 <addr><br/>3408<addr><br/>ac880020</addr></addr> | <flash_row_addr(31:16)></flash_row_addr(31:16)>                                |

|-------------------------------------------------------|--------------------------------------------------------------------------------|

|                                                       | ori t0, \$0,<br><flash_row_addr(15:0)><br/>sw t0,32(a0)</flash_row_addr(15:0)> |

# **Step 3:** Set NVMSRCADDR with the physical source SRAM address.

| ac300040   Sw S0,04(a0) | ac900040 | sw | s0,64(a0) |

|-------------------------|----------|----|-----------|

|-------------------------|----------|----|-----------|

# **Step 4:** Write the operation in NVMCON. Run the unlock sequence using Row Program command.

| ac850000 | sw | a1,0(a0)  |

|----------|----|-----------|

| ac910010 | sw | s1,16(a0) |

| ac910010 | sw | s1,16(a0) |

| ac860008 | sw | a2,8(a0)  |

# **Step 5:** Repeatedly read the NVMCON register and poll for NVMWR bit to get cleared.

| 8c880000 | here1: |                         |

|----------|--------|-------------------------|

| 01064024 | lw     | t0,0(a0)                |

| 1500fffd | and    | t0,t0,a2                |

| 00000000 | bne    | t0,\$0, <here1></here1> |

|          | nop    |                         |

**Step 6:** Delay needed to address B3 ES SI Errata. Wait at least 500 nS after seeing a '0' in

NVMCON<15> before writing to any NVM registers. This requires inserting NOP is the execution.

Example: The following example assumes that the core is executing at 8 MHz, hence 4 NOP instructions equate to 500 nS.

| 00000000 | nop |

|----------|-----|

| 0000000  | nop |

| 00000000 | nop |

| 00000000 | nop |

# PIC32MX

| Step 7: Clear NVMCON.NVMWREN bit.                           |                                                 |                        |

|-------------------------------------------------------------|-------------------------------------------------|------------------------|

| ac870004                                                    | sw                                              | a3,4(a0)               |

| Step 8: Check th                                            | e NVMCO                                         | N.NVMERR bit to ensure |

| that the program sequence completed successfully.           |                                                 |                        |

| If error, jump to e                                         | rror-proces                                     | ssing routine.         |

| 8c880000                                                    | lw                                              | t0,0(a0)               |

| 30082000                                                    | andi                                            | t0,zero,0x2000         |

| 1500 <err_pr< td=""><td>bne</td><td>t0, \$0,</td></err_pr<> | bne                                             | t0, \$0,               |

| OC>                                                         | <err_pr< td=""><td>oc_offset&gt;</td></err_pr<> | oc_offset>             |

| 00000000                                                    | nop                                             |                        |

# 13.2 With PE

When using PE the data is immediately written to the Flash memory from the SRAM. No further action is required.

### 14.0 VERIFY DEVICE MEMORY

The verify step involves reading back the code memory space and comparing it against the copy held in the programmer's buffer. The Configuration registers are verified with the rest of the code.

Note: Because the Configuration registers include the device code protection bit, code memory should be verified immediately after writing if code protection is enabled. This is because the device will not be readable or verifiable if a device Reset occurs after the code-protect bit has been cleared.

### 14.1 Without PE

Reading from Flash memory is performed by executing a series of read accesses from the Fast Data register. Table 19-4 shows the EJTAG programming details, including the address and opcode data for performing processor access operations.

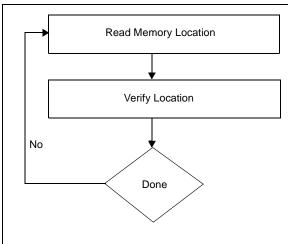

FIGURE 14-1: VERIFYING MEMORY WITHOUT PE

The following steps are required to verify memory:

- 1. XferInstruction (opcode).

- Repeat step 1 until last instruction is transferred to CPU.

- Verify valRead matches copy held in programmers buffer.

- 4. Repeat steps 1-3 for each memory location.

TABLE 14-1: VERIFY DEVICE OPCODES

| Opcode                                                                      | Instruction                                                                                                                          |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Step 1: Initialize                                                          | some constants.                                                                                                                      |

| 3c04bf80                                                                    | lui \$s3, 0xFF20                                                                                                                     |

| Step 2: Read me                                                             | emory Location.                                                                                                                      |

| 3c08 <addr><br/>3508<addr></addr></addr>                                    | <pre>lui \$t0, <falash_word_addr(31:16)>   ori \$t0, <flash_word_addr(15:0)></flash_word_addr(15:0)></falash_word_addr(31:16)></pre> |

| Step 3: Write to                                                            | FastData location.                                                                                                                   |

| 8d090000<br>ae690000                                                        | lw \$t1, 0(\$t0)<br>sw \$t1, 0(\$s3)                                                                                                 |

| <b>Step 4:</b> Read Data from FastData Register 0xFF200000                  |                                                                                                                                      |

| <b>Step 5:</b> Repeat Steps 2-4 until all configuration locations are read. |                                                                                                                                      |

## 14.2 With PE

Memory verify is performed using the GET\_CRC (see Table 16-3) command as shown below.

# FIGURE 14-2: VERIFYING MEMORY WITH PE

The following steps are required to verify memory using the PE:

- 1. XferFastData (GET\_CRC)

- XferFastData (start\_Address)

- 3. XferFastData (length)

- 4. valCkSum = XferFastData (32'h0x0)

- 5. Verify valCkSum matches the checksum of the copy held in the programmers buffer.

# 15.0 EXITING PROGRAMMING MODE

Once a device has been properly programmed, the device must be taken out of Programming mode in order to start proper execution of it's new program memory contents.

### 15.1 4-Wire Interface

Exiting Test mode is done by removing VIH from MCLR, as shown in Figure 15-1. The only requirement for exit is that an interval, P9B, should elapse between the last clock and program signals on PGCx and PGDx before removing VIH.

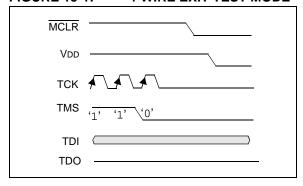

FIGURE 15-1: 4-WIRE EXIT TEST MODE

The following steps are required to exit Test mode:

- 1. SetMode (5'b11111).

- 2. Assert MCLR

- 3. Remove Power (\* if powering device)

### 15.2 2-Wire Interface

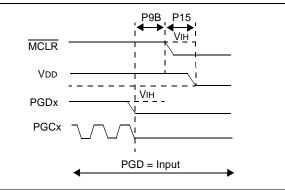

Exiting Test mode is done by removing VIH from  $\overline{MCLR}$ , as shown in Figure 15-2. The only requirement for exit is that an interval, P9B, should elapse between the last clock and program signals on PGCx and PGDx before removing VIH.

### FIGURE 15-2: 2-WIRE EXIT TEST MODE

The following list provides the actual steps required to exit test mode:

- 1. SetMode (5'b11111)

- 2. Assert MCLR

- 3. Issue a clock pulse on PGCx

- 4. Remove Power (\* if powering device)

# 16.0 THE PROGRAMMING EXECUTIVE

# 16.1 Programming Executive Communication

The programmer and programming executive have a master-slave relationship, where the programmer is the master programming device and the programming executive is the slave.

All communication is initiated by the programmer in the form of a command. Only one command at a time can be sent to the programming executive. In turn, the programming executive only sends one response to the programmer after receiving and processing a command.

### 16.1.1 2-WIRE ICSP EJTAG RATE

In Enhanced ICSP mode, the PIC32MX family devices operate from the internal Fast RC oscillator, which has a nominal frequency of 8 MHz. To ensure that the programmer does not clock too fast, it is recommended that a 1 MHz clock be provided by the programmer.

### 16.1.2 COMMUNICATION OVERVIEW

The programmer and the programming executive communicate using the EJTAG address, data and fastdata registers. In particular, the programmer transfers the command and data to the programming executive using the fastdata register. The programmer receives response from the programming executive using the address and data register. The pseudo operation of receiving response is shown in GetPEResponse pseudo operation below:

Format: response = GetPEResponse()

Purpose: The programmer receives 32-bit response value from programming executive.

### **EXAMPLE 16-1: GET PE RESPONSE**

```

WORD GetPEResponse()

WORD response;

// Wait until CPU is ready

SendCommand(ETAP_CONTROL);

// Check if Processor Access bit

(bit 18) is set

do {

controlVal=Xfer-

Data(32'h0x0004C000 );

} while( PrAcc(contorlVal<18>) is

not '1' );

// Select Data Register

SendCommand(ETAP_DATA);

// Receive Response

response = XferData(0);

// Tell CPU to execute instruction

SendCommand(ETAP_CONTROL);

XferData(32'h0x0000C000);

// return 32-bit response

return response;

```

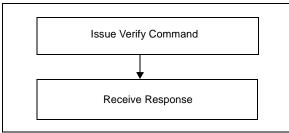

The Table 16-1 shows the typical communication sequence between the programmer and the programming executive. In step 1, the programmer sends the command and optional additional data to the programming executive. Next, the programming executive carries out the command. Once the programming executive finishes execution of command, in step 2, it sends the response back to the programmer. The response may contain more than one response, for example, if the programmer sent a Read command, the response will contain the data read.

TABLE 16-1: COMMUNICATION SEQUENCE FOR PE

| ·                                                                                       |                      |  |

|-----------------------------------------------------------------------------------------|----------------------|--|

| Operation                                                                               | Operand              |  |

| <b>Step 1:</b> Send command and optional data from programmer to programming executive. |                      |  |

| XferFastData                                                                            | (Command   data len) |  |

| XferFastData                                                                            | optional data        |  |

| <b>Step 2:</b> Programmer reads response from programming executive.                    |                      |  |

| GetPEResponse                                                                           | response             |  |

| GetPEResponse                                                                           | response             |  |

# 16.2 Programming Executive Command Set

The programming executive command set is shown in Table 16-3. This table contains the opcode, mnemonic, length, time-out and short description for each command. Functional details on each command are provided in Section 16.2.3 "ROW\_PROGRAM" through Section 16.2.14 "CHANGE\_CFG".

The programming executive sends a response to the programmer for each command that it receives. The response indicates if the command was processed correctly. It includes any required response data or error data.

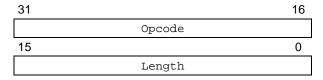

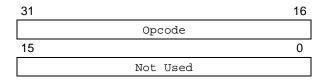

### 16.2.1 COMMAND FORMAT

All programming executive commands have a general format consisting of a 32-bit header and any required data for the command (see Figure 16-1). The 32-bit header consists of a 16-bit opcode field, which is used to identify the command, a 16-bit command length field. The length field indicates the number of bytes to be transferred, if any.

| Note: | Some commands have no Length information, however, the Length field must be |

|-------|-----------------------------------------------------------------------------|

|       | sent and the program executive will ignore                                  |

|       | the data.                                                                   |

### FIGURE 16-1: COMMAND FORMAT

| Command Data High (if required)  15 0                           | 31 |                                 | 16 |

|-----------------------------------------------------------------|----|---------------------------------|----|

| Length (optional)  31 16  Command Data High (if required)  15 0 |    | Opcode                          |    |

| 31 Command Data High (if required) 15 0                         | 15 |                                 | 0  |

| Command Data High (if required)  15 0                           |    | Length (optional)               |    |

| 15 0                                                            | 31 |                                 | 16 |

|                                                                 |    | Command Data High (if required) |    |

|                                                                 | 15 |                                 | 0  |

| Command Data Low (If required)                                  |    | Command Data Low (if required)  |    |

The command Opcode must match one of those in the command set. Any command that is received which does not match the list in Table 16-3 will return a "NACK" response (see **Section 16.2.2** "**Response Format**"

The programming executive uses the command Length field to determine the number of bytes to read from or write. If the value of this field is incorrect, the command will not be properly received by the programming executive.

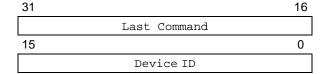

### 16.2.2 RESPONSE FORMAT

The programming executive response set is shown in Table 16-4. All programming executive responses have a general format consisting of a 32-bit header and any required data for the response (see Figure 16-2).

FIGURE 16-2: RESPONSE FORMAT

| 31 |               | 16 |

|----|---------------|----|

|    | Last_Cmd      |    |

| 15 |               | 0  |

|    | Response_Code |    |

| 31 |               | 16 |

|    | Data_High_1   |    |

| 15 |               | 0  |

|    | Data_Low_1    |    |

| 31 |               | 16 |

|    | Data_High_N   |    |

| 15 |               | 0  |

|    | Data_Low_N    |    |

### 16.2.2.1 Last Cmd Field

The Last\_Cmd is a 16-bit field in the first word of the response and indicates the command that the programming executive processed. It can be used to verify that the programming executive correctly received the command that the programmer transmitted.

### 16.2.2.2 Response Code

The response code indicates whether the last command succeeded, failed, or if the command is an un-recognized value. The response code values are shown in Table 16-2.

**TABLE 16-2: RESPONSE VALUES**

| Opcode | Mnemonic | Description                       |

|--------|----------|-----------------------------------|

| 0h     | PASS     | Command successfully processed.   |

| 2h     | FAIL     | Command unsuccessfully processed. |

| 3h     | NACK     | Command not known.                |

### 16.2.2.3 Optional Data

The response header may be followed by optional data in case of certain commands such as read. The number of 32-bit words of optional data varies depending on the last command operation and its parameters.

TABLE 16-3: PROGRAMMING EXECUTIVE COMMAND SET

| Opcode | Mnemonic     | Length*<br>(32-bit<br>words) | Description                                                                    |

|--------|--------------|------------------------------|--------------------------------------------------------------------------------|

| 0h     | ROW_PROGRAM  | 2                            | Program one row of Flash memory at the specified address.                      |

| 1h     | READ         | 2                            | Read N 32-bit words of memory starting from the specified address. (N < 65536) |

| 2h     | PROGRAM      | 130                          | Program Flash memory starting at the specified address.                        |

| 3h     | WORD_PROGRAM | 3                            | Program one word of Flash memory at the specified address.                     |

| 4h     | CHIP_ERASE   | 1                            | Chip Erase of entire chip.                                                     |

| 5h     | PAGE_ERASE   | 2                            | Erase pages of code memory from the specified address.                         |

| 6h     | BLANK_CHECK  | 1                            | Blank Check code.                                                              |

| 7h     | EXEC_VERSION | 1                            | Read the programming executive software version.                               |

| 8h     | GET_CRC      | 2                            | Get CRC of Flash memory.                                                       |

**Legend:** \*Length does not indicate the length of data to be transferred. The Length indicates the size of the command itself, including 32-bit header.

**Note:** One row of code memory consists of (128) 32-bit words. Refer to Table 16-1 for device-specific information.

16.2.3 ROW\_PROGRAM

| FIGURE 16-3:   | ROW  | PROGRAM | <b>COMMAND</b> |

|----------------|------|---------|----------------|

| 1 1001\L 10-3. | TCOM | FIOGIAM |                |

| 31 |             | 16 |

|----|-------------|----|

|    | Opcode      |    |

| 15 |             | 0  |

|    | Length      |    |

| 31 |             | 16 |

|    | Addr_High   |    |

| 15 |             | 0  |

|    | Addr_Low    |    |

| 31 |             | 16 |

|    | Data_High_1 |    |

| 15 |             | 0  |

|    | Data_Low_1  |    |

| 31 |             | 16 |

|    | Data_High_N |    |

| 15 |             | 0  |

|    | Data_Low_N  |    |

| ·  | ·           | ·  |

TABLE 16-4: ROW\_PROGRAM FORMAT

| Field       | Description                                |

|-------------|--------------------------------------------|

| Opcode      | 0h                                         |

| Length      | 128                                        |

| Addr_High   | High 16-bits of 32-bit destination address |

| Addr_Low    | Low 16-bits of 32-bit destination address  |

| Data_High_1 | High 16-bits data word 1                   |

| Data_Low_1  | Low 16-bits data word 1                    |

| Data_High_N | High 16-bits data word 2 through 128       |

| Data_Low_N  | Low 16-bits data word 2 through 128        |

The ROW\_PROGRAM command instructs the programming executive to program a row of data at a specified address.

The data to program to memory, located in command words Data\_1 through Data\_128, must be arranged using the packed instruction word format shown in Table 16-4.

### **Expected Response (1 word):**

FIGURE 16-4: ROW\_PROGRAM RESPONSE

| 31 |              | 16 |

|----|--------------|----|

|    | Last Command |    |

| 15 |              | 0  |

|    |              |    |

16.2.4 READ

FIGURE 16-5: READ COMMAND

| 31 |           | 16 |

|----|-----------|----|

|    | Opcode    |    |

| 15 |           | 0  |

|    | Length    |    |

| 31 |           | 16 |

|    | Addr_High |    |

| 15 |           | 0  |

|    | Addr_Low  |    |

**TABLE 16-5: READ FORMAT**

| Field     | Description                                    |

|-----------|------------------------------------------------|

| Opcode    | 1h                                             |

| Length    | Number of 32-bit words to read (max. of 65535) |

| Addr_Low  | Low 16-bits of 32-bit source address           |

| Addr_High | High 16-bits of 32-bit source address          |

The Read command instructs the programming executive to read Length 32-bit words of Flash memory, including Configuration Words, starting from the 32-bit address specified by Addr\_Low and Addr\_High. This command can only be used to read 32-bit data. All data returned in response to this command uses the packed data format as shown in Table 16-5.

### **Expected Response:**

FIGURE 16-6: READ RESPONSE

| 31 |              | 16 |

|----|--------------|----|

|    | Last Command |    |

| 15 |              | 0  |

|    | Return Code  |    |

| 31 |              | 16 |

|    | Data High    |    |

| 15 |              | 0  |

|    | Data Low     |    |

Note: Reading unimplemented memory will cause the programming executive to reset. Please ensure that only memory locations present on a particular device are accessed.

### 16.2.5 PROGRAM

### FIGURE 16-7: PROGRAM COMMAND

| 31 |             | 16 |

|----|-------------|----|

|    | 0pcode      |    |

| 15 |             | 0  |

|    | Not Used    |    |

| 31 |             | 16 |

|    | Addr_High   |    |

| 15 |             | 0  |

|    | Addr_Low    |    |

| 31 |             | 16 |

|    | Length_High |    |

| 15 |             | 0  |

|    | Length_Low  |    |

| 31 |             | 16 |

|    | Data_High_N |    |

| 15 |             | 0  |

|    | Data_Low_N  |    |

TABLE 16-6: PROGRAM FORMAT

| Field       | Description                                |

|-------------|--------------------------------------------|

| Opcode      | 2h                                         |

| Addr_Low    | Low 16-bits of 32-bit destination address  |

| Addr_High   | High 16-bits of 32-bit destination address |

| Length_Low  | Low 16-bits of Length                      |

| Length_High | High 16-bits Length                        |

| Data_Low_N  | Low 16-bits data word 2 through N          |

| Data_High_N | High 16-bits data word 2 through N         |

The Program command instructs the programming executive to program Flash memory, including Configuration Words, starting from the 32-bit address specified by Addr\_Low and Addr\_High. The address must be aligned to 512 byte boundary (aligned to flash row size). Also, the length must be multiple of 512 bytes (multiple of Flash row size).

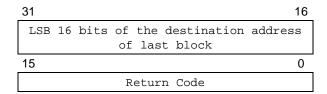

The response for this command is little different than the other commands. The 16 MSbs of the response contains the 16 LSbs of the destination address where the last block is programmed. This helps the probe and PE maintain proper synchronization of data and responses.

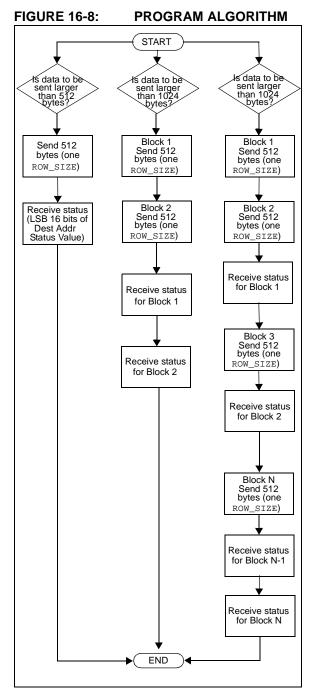

There are three programming scenarios:

- 1. The data to be programmed is 512 bytes long.

- 2. The data to be programmed is 1024 bytes.

- The data to be programmed is larger than 1024 bytes.

When the data length is equal to 512 bytes, the PE will send the response of this command immediately after receiving the 512 bytes.

When the length is 1024 bytes, the PE will receive the first two blocks of 512-byte data continuously. Next, the PE responds with the status of the write operation of the first 512-byte block, followed immediately by the status of the write operation of the second 512-byte block.

If the data to be programmed is larger than 1024 bytes, the first two 512-byte blocks are sent consecutively followed by the response for block 1. Next, the 3rd 512-byte block is sent, followed by the response for block 2 is received. The successive blocks and responses are exchanged in similar fashion. After sending the last 512-byte block, the probe shall receive the response for the second to last block, followed by the response for the last block.

If the PE encounters an error in programming any of the blocks, it sends a failure status to the probe. Upon receiving the failure status, the probe must stop sending any further data. The PE will not receive any further data for this command from the probe.

Note: If the Program command fails, the programmer should read the failing row using the Read command from the Flash memory. Next, the programmer should compare the row received from Flash memory to its local copy word-by-word to determine the address where Flash programming fails.

The Figure 16-8 shows the programming concept.

**Expected Response (1 word):**

### FIGURE 16-9: PROGRAM RESPONSE

16.2.6 WORD\_PROGRAM

# FIGURE 16-10: WORD\_PROGRAM COMMAND

| 31 |           | 16 |

|----|-----------|----|

|    | Opcode    |    |

| 15 |           | 0  |

|    | Length    |    |

| 31 |           | 16 |

|    | Addr_High |    |

| 15 |           | 0  |

|    | Addr_Low  |    |

| 31 |           | 16 |

|    | Data_High |    |

| 15 |           | 0  |

|    | Data_Low  |    |

TABLE 16-7: WORD-PROGRAM FORMAT

| Field     | Description                                |

|-----------|--------------------------------------------|

| Opcode    | 3h                                         |

| Length    | 2                                          |

| Addr_High | High 16 bits of 32-bit destination address |

| Addr_Low  | Low 16 bits of 32-bit destination address  |

| Data_High | High 16 bits data word                     |

| Data_Low  | Low 16 bits data word                      |

The WORD\_PROGRAM command instructs the programming executive to program a 32-bit word of data at the specified address.

### **Expected Response (1 word):**

FIGURE 16-11: WORD\_PROGRAM RESPONSE

| 31 |              | 16 |

|----|--------------|----|

|    | Last Command |    |

| 15 |              | 0  |

|    | Return Code  |    |

16.2.7 CHIP\_ERASE

### FIGURE 16-12: CHIP\_ERASE COMMAND

| 31 |        | 16 |

|----|--------|----|

|    | Opcode |    |

| 15 |        | 0  |

|    | Length |    |

TABLE 16-8: CHIP\_ERASE FORMAT

| Field     | Description                                |

|-----------|--------------------------------------------|

| Opcode    | 4h                                         |

| Length    | Ignored                                    |

| Addr_Low  | Low 16 bits of 32-bit destination address  |

| Addr_High | High 16 bits of 32-bit destination address |

The CHIP\_ERASE command erases the entire chip including the configuration block.

After the erase is performed, the entire Flash memory contains 0xFFFF\_FFFF.

### **Expected Response (1 word):**

FIGURE 16-13: CHIP\_ERASE RESPONSE

| 31 |              | 16 |

|----|--------------|----|

|    | Last Command |    |

| 15 |              | 0  |

|    | Return Code  |    |

16.2.8 PAGE\_ERASE

### FIGURE 16-14: PAGE\_ERASE COMMAND

| 31 |           | 16 |

|----|-----------|----|

|    | Opcode    |    |

| 15 |           | 0  |

|    | Length    |    |

| 31 |           | 16 |

|    | Addr_High |    |

| 15 |           | 0  |

|    | Addr_Low  |    |

TABLE 16-9: PAGE\_ERASE FORMAT

| Field     | Description                                |

|-----------|--------------------------------------------|

| Opcode    | 5h                                         |

| Length    | Number of pages to erase                   |

| Addr_Low  | Low 16 bits of 32-bit destination address  |

| Addr_High | High 16 bits of 32-bit destination address |

The PAGE\_ERASE command erases the specified number of pages of code memory from the specified base address. The specified base address must be a multiple of 0x400.

After the erase is performed, all targeted words of code memory contain 0xFFFF\_FFFF.

### **Expected Response (1 word):**

## FIGURE 16-15: PAGE\_ERASE RESPONSE

| 31 |              | 16 |

|----|--------------|----|

|    | Last Command |    |

| 15 |              | 0  |

|    | Return Code  |    |

16.2.9 BLANK\_CHECK

## FIGURE 16-16: BLANK\_CHECK COMMAND

| 31 |             | 16 |

|----|-------------|----|

|    | Opcode      |    |

| 15 |             | 0  |

|    | Not Used    |    |

| 31 |             | 16 |

|    | Addr_High   |    |

| 15 |             | 0  |

|    | Addr_Low    |    |

| 31 |             | 16 |

|    | Length_High |    |

| 15 |             | 0  |

|    | Length_Low  |    |

### TABLE 16-10: BLANK\_CHECK FORMAT

| Field   | Description                                                   |

|---------|---------------------------------------------------------------|

| Opcode  | 6h                                                            |

| Length  | Number of program memory locations to check in terms of bytes |

| Address | Address where to start the Blank Check                        |

The BLANK\_CHECK command queries the programming executive to determine if the contents of code memory and code-protect Configuration bits (GCP and GWRP) are blank (contains all '1's).

### Expected Response (1 word for blank device):

# FIGURE 16-17: BLANK\_CHECK RESPONSE

| 31 |              | 16 |

|----|--------------|----|

|    | Last Command |    |

| 15 |              | 0  |

|    | Return Code  |    |

16.2.10 EXEC\_VERSION

FIGURE 16-18: EXEC\_VERSION COMMAND

### TABLE 16-11: EXEC\_VERSION FORMAT

| Field  | Description |

|--------|-------------|

| Opcode | 7h          |

| Length | Ignored     |

The EXEC\_VERSION command queries the version of the programming executive software stored in RAM.

The version value of the current Programming Executive is 0x0105.

### **Expected Response (1 word):**

FIGURE 16-19: EXEC\_VERSION RESPONSE

| 31 |              | 16 |

|----|--------------|----|

|    | Last Command |    |

|    |              |    |

| 15 |              | 0  |

16.2.11 GET\_CRC

### FIGURE 16-20: GET\_CRC COMMAND

| 31 |             | 16 |

|----|-------------|----|

|    | Opcode      |    |

| 15 |             | 0  |

|    | Not Used    |    |

| 31 |             | 16 |

|    | Addr_High   |    |

| 15 |             | 0  |

|    | Addr_Low    |    |

| 31 |             | 16 |

|    | Length_High |    |

| 15 |             | 0  |

|    | Length_Low  | ·  |

TABLE 16-12: GET\_CRC FORMAT

| Field   | Description                                                   |

|---------|---------------------------------------------------------------|

| Opcode  | 8h                                                            |

| Address | Address where to start calculating CRC                        |

| Length  | Length of buffer on which to calculate CRC in number of bytes |

The GET\_CRC command calculates the CRC of the buffer from the specified address to the specified length, using the table look-up method.

The CRC details are as follows:

CRC-CCITT, 16-bit

polynomial: X^16+X^12+X^5+1, hex= 0x00011021

seed: 0xFFFF

MSB shifted in first.

Note that in the response, only the CRC LSB 16-bit are  $\,$

GET CRC RESPONSE

valid.

Expected Response (2 words):

FIGURE 16-21:

### . . ,

| 31 |              | 16 |

|----|--------------|----|

|    | Last Command |    |

| 15 |              | 0  |

|    | Return Code  |    |

| 31 |              | 16 |

|    |              |    |

|    | CRC_High     |    |

| 15 | CRC_High     | 0  |

16.2.12 PROGRAM\_CLUSTER

FIGURE 16-22: PROGRAM\_CLUSTER COMMAND

| 31 |             | 16 |

|----|-------------|----|

|    | Opcode      |    |

| 15 |             | 0  |

|    | Not Used    |    |

| 31 |             | 16 |

|    | Addr_High   |    |

| 15 |             | 0  |

|    | Addr_Low    |    |

| 31 |             | 16 |

|    | Length_High |    |

| 15 |             | 0  |

|    | Length_Low  |    |

TABLE 16-13: PROGRAM\_CLUSTER FORMAT

| Field   | Description                                                   |

|---------|---------------------------------------------------------------|

| Opcode  | 9h                                                            |

| Address | Address where to start calculating CRC                        |

| Length  | Length of buffer on which to calculate CRC in number of bytes |

The PROGRAM\_CLUSTER command programs the specified number of bytes to the specified address. The address must be 32-bit aligned, and the number of bytes must be integral multiple of 32-bit word.

| Note: | If Program command fails, the program-    |

|-------|-------------------------------------------|

|       | mer should read the failing row using the |

|       | Read command from the Flash memory.       |

|       | Next, the programmer should compare the   |

|       | row received from Flash memory to its     |

|       | local copy word-by-word to determine the  |

|       | address where Flash programming fails.    |

**Expected Response (1 word):**

FIGURE 16-23: PROGRAM\_CLUSTER RESPONSE

| 31 |              | 16 |

|----|--------------|----|

|    | Last Command |    |

| 15 |              | 0  |

|    | Return Code  |    |

16.2.13 GET\_DEVICEID

FIGURE 16-24: GET\_DEVICEID COMMAND

TABLE 1: GET\_DEVICEID FORMAT

| Field  | Description |

|--------|-------------|

| Opcode | Ah          |

The  ${\tt GET\_DEVICEID}$  command returns the hardware ID of the device.

**Expected Response (1 word):**

FIGURE 16-25: GET\_DEVICEID

**RESPONSE**

16.2.14 CHANGE\_CFG

FIGURE 16-26: CHANGE\_CFG COMMAND

| 31 |              | 16 |

|----|--------------|----|

|    | Opcode       |    |