|

Группа компонентов

ARM

Основные параметры

| ЦПУ: Ядро |

Cortex-A5

|

| ЦПУ: DSP |

Да

|

| ЦПУ: FPU |

Да

|

| ЦПУ: F,МГц |

от 0 до 536

|

| Память: RAM,КБайт |

128

|

| I/O (макс.),шт. |

160

|

| Таймеры: 32-бит,шт |

6

|

| Таймеры: Каналов ШИМ,шт |

4

|

| Таймеры: RTC |

Да

|

| Интерфейсы: UART,шт |

7

|

| Интерфейсы: SPI,шт |

6

|

| Интерфейсы: I2C,шт |

3

|

| Интерфейсы: USB,шт |

3

|

| Интерфейсы: CAN,шт |

2

|

| Интерфейсы: Ethernet,шт |

2

|

| Интерфейсы: LIN,шт |

4

|

| Аналоговые входы: Разрядов АЦП,бит |

12

|

| Аналоговые входы: Каналов АЦП,шт |

12

|

| Аналоговые входы: Быстродействие АЦП,kSPS |

440

|

| VCC,В |

от 1.8 до 3.3

|

| ICC,мА |

88

|

| TA,°C |

от -40 до 105

|

| Корпус |

LFBGA-324

|

Общее описание

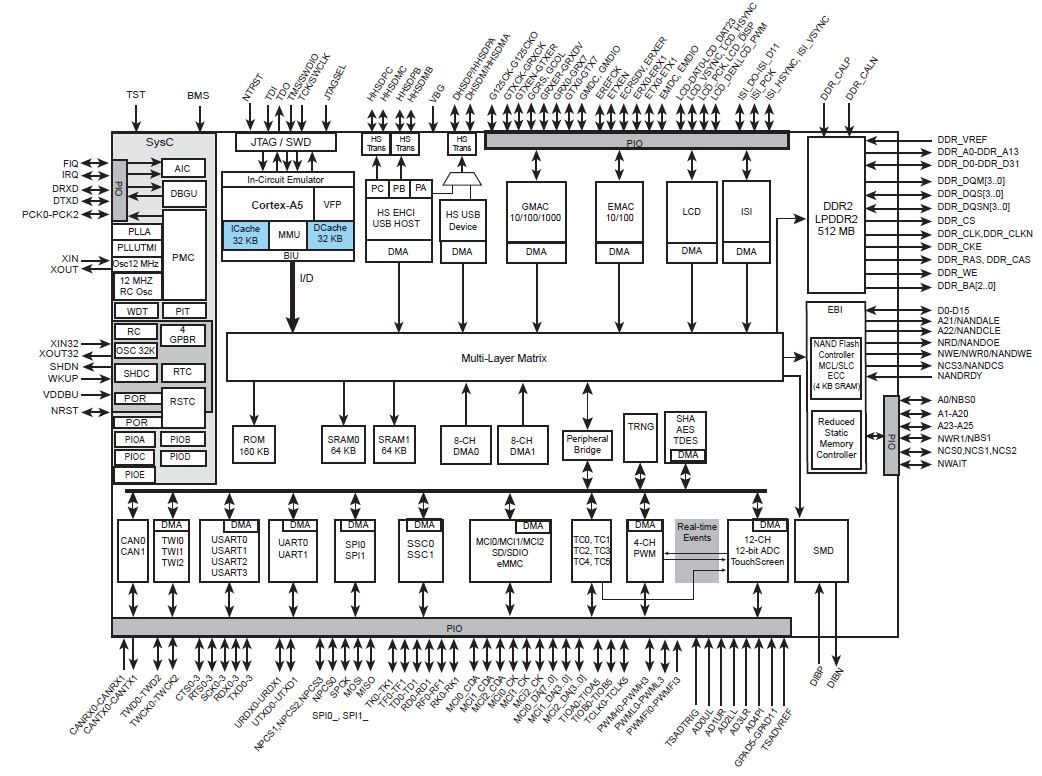

Отличительные особенности:

- Ядро

- Процессор ARM® Cortex™-A5 с набором инструкций ARM v7-A Thumb2®

- Частота ядра до 536 МГц

- Кэш-память данных 32 Кбайт, кэш-память инструкций 32 Кбайт, виртуальная архитектура системной памяти (VMSA)

- Полностью интегрированные устройство управления памятью (MMU) и модуль вычислений с плавающей точкой (VFPv4)

- Память

- 160 Кбайт однократно-программируемой (ROM) памяти, доступ за один такт на частоте системы. Встроенный загрузчик: загрузка с NAND FLASH носителей, карт памяти SDCard и eMMC, последовательной FLASH-памяти DataFlash®, определяемый порядок загрузки.

- 128 Кбайт SRAM-памяти, доступ за один такт на частоте системы.

- Широкополосный 32-битный многопортовый контроллер динамической памяти, поддержка до 8 банков по 512 Мбайт DDR2/LPDDR/LPDDR2 типа.

- Независимый контроллер статической памяти с поддержкой NAND FLASH памяти SLC/MLC типов с 24-битным кодом коррекции ошибок (PMECC)

- Система с рабочей частотой до 166 МГц

- Схема сброса по включению питания, контроллер сброса (перезагрузки), контроллер выключения питания, таймер периодических интервалов, сторожевой таймер и часы реального времени.

- Выбор настроек режима загрузки, команда процедуры перераспределения (remapping) памяти.

- Малопотребляющий RC-генератор на 32 кГц и высокоскоростные RC-генераторы на 12 МГц.

- Одна система фазовой автоподстройки частоты (PLL) на 400...1000 MГц для тактирования системы, и одна на 480 MГц для высокоскоростного USB интерфейса.

- 39-канальный контроллер прямого доступа к памяти (DMA), включая два 8-канальных 64-битных центральных контроллера.

- 64-битный улучшенный контроллер прерываний.

- Три внешних программируемых тактовых сигналов.

- Программируемый блок плавких перемычек с 256 конфигурационными битами, 192 из них доступны пользователю.

- Система управления пониженным энергопотреблением

- Контроллер выключения питания

- Регистры резервного питания от аккумулятора

- Генератор тактового сигнала и контроллер управления питанием

- Режим сверхнизкой тактовой частоты, возможности программной оптимизации энергопотребления

- Периферийные устройства.

- Контроллер TFT ЖКИ с функциями видеоналожения, альфа-смешивания, поворота, масштабирования и преобразования цветового пространства.

- Интерфейс датчика изображения ITU-R BT. 601/656

- 3-канальный контроллер USB интерфейса с поддержкой высокоскоростного, скоростного и низкоскоростного (FS/HS/LS) режимов с интегрированным приемопередатчиком

- Один контроллер устройства

- Один хост-контроллер с интегрированным корневым концентратором (три нисходящих порта)

- Один Gigabit Ethernet контроллер (GMAC, скорость передачи 10/100/1000 Мбит/с) с поддержкой IEEE1588

- Один Ethernet контроллер со скоростью передачи данных 10/100 Мбит/с (EMAC)

- Два CAN-контроллера с 8 буферами сообщений, полностью совместимые со спецификациями CAN 2.0 Part A и 2.0 Part B

- Интерфейс программно реализованного модема

- 3-канальный хост-контроллер карт памяти (eMMC 4.3 и SD 2.0)

- Два последовательных периферийных интерфейса SPI с поддержкой режимов ведущий/ведомый (Master/Slave)

- Два синхронных последовательных интерфейса

- Три двухпроводных интерфейса со скоростью передачи данных до 400Кбит/с и поддержкой протоколов I2C и SMBUS

- Четыре универсальных синхронно-асинхронных приёмопередатчика USART, два универсальных асинхронных приёмопередатчика UART, один модуль внутрисхемной отладки DBGU.

- Два 3-канальных 32-битных таймера/счётчика.

- Один 4-канальный 16-битный модуль широтно-импульсной модуляции.

- Один 12-канальный 12-битный АЦП с поддержкой резистивного сенсорного экрана

- Регистры с защитой от записи

- Безопасность

- Генератор действительно случайных чисел (TRNG)

- Модуль шифрования

- AES: алгоритм шифрования с 256-/192-/128-битными ключами, совместим со спецификацией FIPS PUB 197

- TDES: алгоритм шифрования с двумя или тремя ключами, совместим со спецификацией FIPS PUB 46-3.

- SHA: Поддерживает алгоритм безопасного хеширования (SHA1, SHA224, SHA256, SHA384, SHA512)

- Защищенный загрузчик компании Atmel®

- Линии ввода/вывода

- Пять 32-битных контроллеров параллельного ввода/вывода

- 160 линий ввода/вывода

- Генерация сигнала прерывание по изменению состояния входа для каждой линии ввода/вывода, произвольный триггер Шмидта на входе.

- Индивидуально программируемые линии ввода/вывода (с открытым стоком, подтягиваяющий (pull-up) и согласующий (pull-down) резистор), синхронный выход, схема фильтрации.

- Контроль скорости нарастания выходного напряжения на высокоскоростных линиях ввода/вывода.

- Контроль сопротивления на линиях ввода/вывода DDR памяти.

- Корпус

- 324-выводной корпус BGA (массив шариковых выводов), шаг выводов 0.8 мм.

|

Datasheet

SAMA5D3 (7.6 Мб), 14.11.2013 SAMA5D3 (7.6 Мб), 14.11.2013

Производитель

Где купить

Дистрибуторы

Дилеры

Где купить ещё

|

SAMA5D3 (7.6 Мб), 14.11.2013

SAMA5D3 (7.6 Мб), 14.11.2013

SAMA5D3 Семейство микропроцессоров SAMA5D3, выполненных на базе ядра ARM® Cortex™-A5 (7.6 Мб), 14.11.2013

SAMA5D3 Семейство микропроцессоров SAMA5D3, выполненных на базе ядра ARM® Cortex™-A5 (7.6 Мб), 14.11.2013

SAMA5D3 Семейство микропроцессоров SAMA5D3, выполненных на базе ядра ARM® Cortex™-A5. Краткое описание (558.9 Кб), 14.11.2013

SAMA5D3 Семейство микропроцессоров SAMA5D3, выполненных на базе ядра ARM® Cortex™-A5. Краткое описание (558.9 Кб), 14.11.2013

Архитектура и система команд RISС-процессоров семейства ARM (Рус)

Архитектура и система команд RISС-процессоров семейства ARM (Рус)