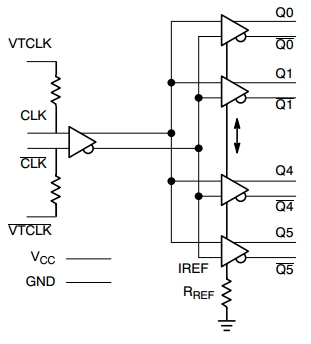

NB3N106K Дифференциальный буфер с напряжением 3.3 В, HCSL выходы

|

Блок-схема  Группа компонентов ИС тактирования и синхронизацииОсновные параметры

Общее описаниеДифференциальные буферы с разветвлением на выходе NB3N106K, NB3N108K, NB3N111K и NB3N121K предназначены для построения разветвленных структур тактирования, а также драйверов–формирователей идентичных дифференциальных сигналов данных. Устройства обеспечивают, соответственно, 6, 8, 10 или 21 выходных каналов передачи информации и идеально подходят для систем, требующих нескольких копий сигнала с высокой точностью и низким показателем дрожания фронтов сигнала. Типовое значение среднеквадратичного аддитивного фазового джиттера составляет всего 0.1 пс (в диапазоне частот от 12 кГц до 20 МГц), что в сочетании с малым различием момента изменения сигнала на параллельных выходах (не более 100 пс) позволяет использовать новые высокопроизводительные разветвляющие буферы в приложениях с высокоскоростным интерфейсом PCI Express поколений I, II и III. Входы устройств допускают прямое подключение к несимметричным или дифференциальным источникам сигнала форматов LVPECL (низковольтной положительной эмиттерно-связанной логики), LVDS (низковольтной передачи дифференциальных сигналов) и HCSL (высокоскростной логики с токовым управлением), обеспечивая максимальную конструкторскую гибкость и позволяя разработчикам с легкостью использовать различные виды входных сигнальных интерфейсов. Кроме того, представленное семейство буферов с разветвлением на выходе идеально дополняет семейство высокочастотных прецизионных тактовых генераторов с низким джиттером NB3N3002 и NB3N5573 для приложений с интерфейсом PCI Express, позволяя создавать разветвленные структуры тактирования разнообразных систем. |

NB3N106K (152.7 Кб), 30.11.2012 NB3N106K (152.7 Кб), 30.11.2012

|

Datasheet

NB3N106K Дифференциальный буфер с напряжением 3.3 В, HCSL выходы (152.7 Кб), 30.11.2012

NB3N106K Дифференциальный буфер с напряжением 3.3 В, HCSL выходы (152.7 Кб), 30.11.2012

| Автор документа: Жанна Свирина, Кол-во просмотров: 1032 |

Дата публикации: 30.11.2012 08:40 Дата редактирования: 30.11.2012 08:41 |