|

Группа компонентов

Сигнальные Процесоры

Основные параметры

| ЦПУ: Ядро |

e500

|

| ЦПУ: F,МГц |

от 0.667 до 1200

|

| Память: Flash,КБайт |

64

|

| Таймеры: RTC |

Нет

|

| Интерфейсы: UART,шт |

2

|

| Интерфейсы: SPI,шт |

1

|

| Интерфейсы: I2C,шт |

4

|

| Интерфейсы: USB,шт |

2

|

| Интерфейсы: Ethernet,шт |

5

|

| Корпус |

FCPBGA-783

|

Общее описание

Отличительные особенности:

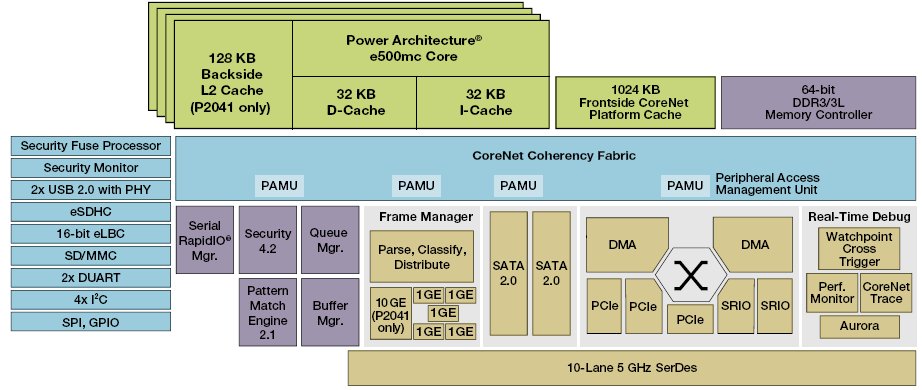

- Четыре высокопроизводительных ядра e500mc, выполненных по технологии Power Architecture®, с рабочей частотой до 1.2 ГГц

- 32 КБайт кэш-памяти инструкций и 32 КБайт кэш-памяти данных первого уровня (L1) для каждого ядра

- Три уровня инструкций: пользователь, супервизор, гипервизор

- Независимые схемы начальной загрузки и сброса

- Функция защищенной загрузки

- 1 МБайт системной кэш-памяти платформы CoreNet (CPC)

- Иерархическая структура обмена данными

- Структура CoreNet с поддержкой когерентных и некогерентных транзакций с назначениями приоритетов и распределением полосы пропускания между оконечными устройствами CoreNet

- Структура менеджера очереди с поддержкой управления очереди пакетного уровня и диспетчеризации по уровню обслуживания

- Один 64-битный контроллер DDR3/DDR3L SDRAM памяти с кодом коррекции ошибок (ECC) и поддержкой чередования банков памяти

- Ускоритель тракта данных, включающий функции ускорения следующих функций:

- Парсинг, классификация и распределение пакетов

- Управление очередью с диспетчеризацией, установкой последовательности пакетов и отслеживанием перегрузок

- Аппаратное управление буфером

- Кодирование/декодирование (SEC 4.2)

- Модуль сопоставления с образом регулярных выражений (PME 2.1)

- Менеджер обмена сообщениями интерфейса RapidIO (RMan)

- Контроллер интерфейса Ethernet

- Пять каналов 1 Гбит/с или четыре канала 2.5 Гбит/с

- Высокоскоростные периферийные интерфейсы

- Три контроллера PCI Express 2.0 с максимальной скоростью до 5 Гбит/с

- Два контроллера RapidIO версии 1.3 с поддержкой возможностей версии 2.1 и максимальной скоростью до 5 Гбит/с

- Менеджер обмена сообщениями интерфейса RapidIO с поддержкой классов 5-6 и 8-11

- Два канала SATA 2.0 с поддержкой скоростей передачи данных 1.5 Гбит/с (SATA I) и 3 Гбит/с (SATA II)

- Дополнительные периферийные интерфейсы

- Два контроллера USB 2.0 с интегрированным физическим уровнем

- Контроллер карт памяти SD/MMC (eSDHC)

- Расширенный контроллер SPI

- Четыре контроллера I2C

- Два контроллера DUART

- 10-канальная схема параллельно-последовательного/ последовательно-параллельного преобразования (SerDes) с рабочей частотой до 5 ГГц

- Расширенный контроллер локальной шины (eLBC)

- Программируемый контроллер прерываний (PIC) для многоядерной архитектуры

- Два 4-канальных контроллера прямого доступа к памяти (DMA)

- 783-выводной корпус FCPBGA, размером 23 х 23 мм

|

Datasheet

P2 Series (252.3 Кб), 18.11.2011 P2 Series (252.3 Кб), 18.11.2011

Производитель

Где купить

Дистрибуторы

Дилеры

Где купить ещё

|

P2 Series (252.3 Кб), 18.11.2011

P2 Series (252.3 Кб), 18.11.2011

P2 Series 4-ядерный коммуникационный процессор QorIQ серии P2 (252.3 Кб), 18.11.2011

P2 Series 4-ядерный коммуникационный процессор QorIQ серии P2 (252.3 Кб), 18.11.2011