|

Группа компонентов

Сигнальные Процесоры

Основные параметры

| ЦПУ: Ядро |

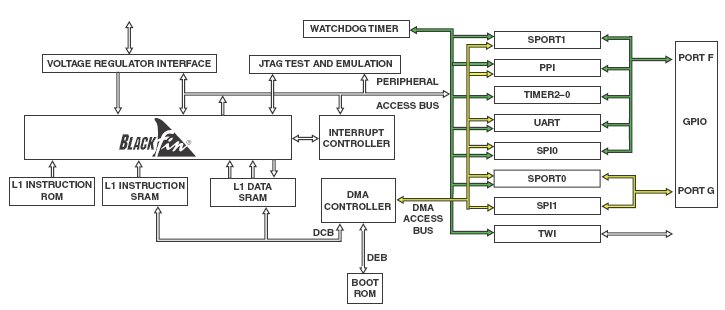

Blackfin

|

| ЦПУ: F,МГц |

от 0 до 400

|

| Память: RAM,КБайт |

68

|

| I/O (макс.),шт. |

32

|

| Таймеры: 32-бит,шт |

4

|

| Таймеры: Каналов ШИМ,шт |

3

|

| Таймеры: RTC |

Нет

|

| Интерфейсы: UART,шт |

2

|

| Интерфейсы: SPI,шт |

2

|

| Интерфейсы: DMA,шт |

11

|

| VCC,В |

от 1.16 до 1.47

|

| ICC,мА |

55

|

| TA,°C |

от -40 до 85

|

| Корпус |

LFCSP-64

|

Общее описание

Отличительные особенности:

- Общие:

- Ядро Blackfin частотой до 400 МГц производительностью 800 MMACS, содержащее два 16-разрядных умножителя, два 40-рязрядных АЛУ, четыре 8-разрядных видео АЛУ, 40-разрядный регистр сдвига;

- RISC-подобная архитектура регистров и набор инструкций;

- Продвинутые средства отладки трассировки и профилирования;

- Широкий выбор напряжений питания для портов ввода/вывода;

- Потребляемая мощность 88 мВт на частоте 300 МГц;

- Широкий выбор напряжений питания, поддерживаемых процессором для портов ввода/вывода;

- Функция управления внешним источником питания;

- 64-контактный (9×9мм) LFCSP корпус;

- Диапазоны рабочих температур: 0…+70 °С или -40…+85 °С

- Память:

- 68 килобайт L1-памяти (ОЗУ ядра процессора);

- Гибкие настройки для boot-загрузки с внешней флэш-памяти, также через SPI, PPI или UART порты;

- Поддержка механизмов защиты памяти и кэширования.

- Периферия:

- Четыре 32-разрядных счетчиков-таймеров, три из них с поддержкой ШИМ;

- Два двухканальных полнодуплексных синхронных последовательных порта (SPORT) с поддержкой восьми стерео I2S каналов;

- Два последовательных порта SPI;

- Два UART порта с поддержкой IrDA®;

- Параллельный интерфейс PPI с поддержкой видеорежимов ITU-R 656;

- Двухпроводный интерфейс TWI;

- 9 каналов DMA периферия-память;

- 2 канала DMA память-память;

- 28 прерывания в контроллере событий;

- 32 выводов общего назначения с программируемым гистерезисом;

- Отладочный интерфейс JTAG;

- Программное управление частотой ядра с помощью встроенного умножителя на синтезаторе ФАПЧ.

|

Datasheet

ADSP-BF592 (1.6 Мб), 08.09.2011 ADSP-BF592 (1.6 Мб), 08.09.2011

Производитель

Где купить

Дистрибуторы

Дилеры

Где купить ещё

|

ADSP-BF592 (1.6 Мб), 08.09.2011

ADSP-BF592 (1.6 Мб), 08.09.2011

ADSP-BF592 Сигнальный процессор семейства Blackfin (1.6 Мб), 08.09.2011

ADSP-BF592 Сигнальный процессор семейства Blackfin (1.6 Мб), 08.09.2011