|

Группа компонентов

Сигнальные Процесоры

Основные параметры

| ЦПУ: Ядро |

e500

|

| ЦПУ: F,МГц |

от 533 до 800

|

| Память: RAM,КБайт |

256

|

| I/O (макс.),шт. |

32

|

| Таймеры: RTC |

Нет

|

| Интерфейсы: UART,шт |

2

|

| Интерфейсы: SPI,шт |

1

|

| Интерфейсы: I2C,шт |

2

|

| Интерфейсы: USB,шт |

2

|

| Интерфейсы: Ethernet,шт |

3

|

| Интерфейсы: DMA,шт |

4

|

| TA,°C |

от 0 до 125

|

| Корпус |

TEPBGA-425

|

Общее описание

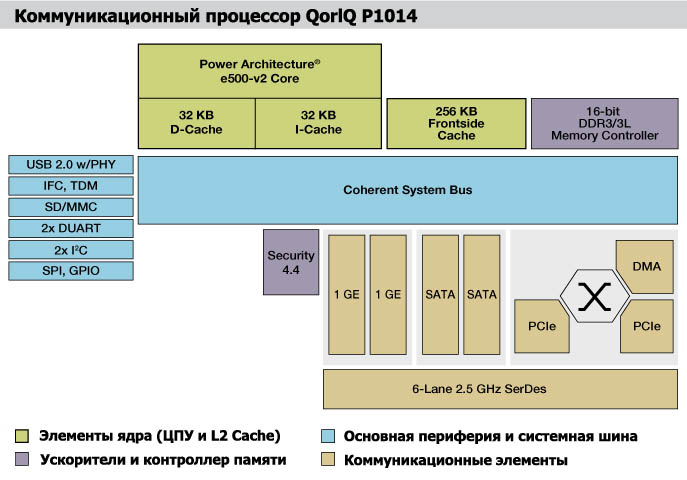

Отличительные особенности:

- Одноядерный процессор с ядром e500 Power Architecture®

- Рабочая частота ядра от 533 МГц до 800 МГц

- 32 КБайт кэш-память инструкций первого уровня и 32 КБацт кэш-память данных первого уровня

- 256 КБайт кэш-память второго уровня с кодом коррекции ошибок (ECC), также конфигурируемая как SRAM данных и резервная память

- Три контроллера enhanced Ethernet 10/100/1000 Мбит/с

- Поддержка протокола IEEE® 1588

- Шесть мультиплексированных контроллеров SerDes (параллельно-последовательная/последовательно-параллельная передача данных) с частотой до 3.125 ГГц

- Два контроллера PCI Express

- Два контроллера SGMII

- Два канала SATA

- Контроллер интерфейса USB 2.0 с интегрированным физическим уровнем и поддержкой режимов ведущий, ведомый и OTG

- SPI интерфейс

- Платформа доверенной загрузки (только P1010), интегрированный модуль защиты

- 16-/32-битный контроллер памяти SDRAM DDR3 с кодом коррекции ошибок (ECC)

- 4-канальный контроллер прямого доступа к памяти (DMA)

Контроллер FlexCAN

|

Datasheet

P1010, P1014 (204 Кб), 01.09.2011 P1010, P1014 (204 Кб), 01.09.2011

Производитель

Где купить

Дистрибуторы

Дилеры

Где купить ещё

|

P1010, P1014 (204 Кб), 01.09.2011

P1010, P1014 (204 Кб), 01.09.2011

P1010, P1014 Коммуникационные процессоры семейства QorlQ (204 Кб), 01.09.2011

P1010, P1014 Коммуникационные процессоры семейства QorlQ (204 Кб), 01.09.2011