|

Группа компонентов

ColdFire

Основные параметры

| ЦПУ: Ядро |

ColdFire

|

| ЦПУ: F,МГц |

от 0 до 250

|

| Память: RAM,КБайт |

64

|

| I/O (макс.),шт. |

87

|

| Таймеры: RTC |

Да

|

| Интерфейсы: UART,шт |

10

|

| Интерфейсы: SPI,шт |

4

|

| Интерфейсы: I2C,шт |

6

|

| Интерфейсы: CAN,шт |

2

|

| Интерфейсы: Ethernet,шт |

2

|

| Интерфейсы: DMA,шт |

1

|

| Аналоговые входы: Разрядов АЦП,бит |

12

|

| Аналоговые выходы: Разрядов ЦАП,бит |

12

|

| VCC,В |

от 1.8 до 3.3

|

| TA,°C |

от -40 до 85

|

| Корпус |

MAPBGA-256

|

Общее описание

Отличительные особенности

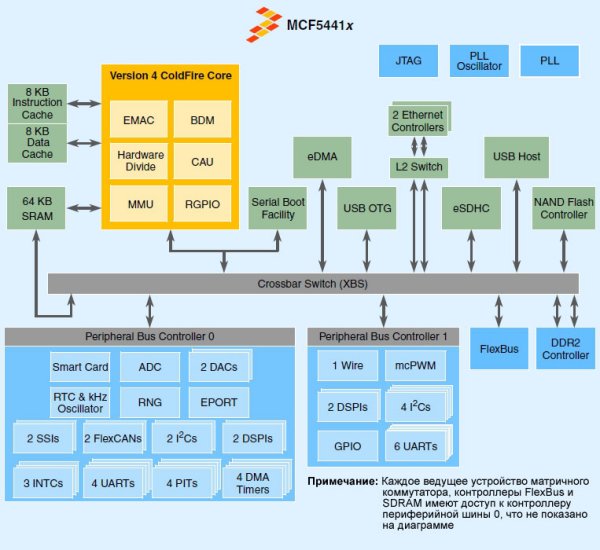

- Процессорное ядро ColdFire® версии 4 с контроллером доступа к среде Ethernet (EMAC) и блоком управления памятью (MMU)

- Производительность до 385 Dhrystone 2.1 MIPS на частоте 250 МГц

- 8 КБайт кэш-памяти инструкций и 8 КБайт кэш-памяти данных

- 64 КБайт внутренней SRAM-памяти, с двухпортовым соединением с локальной шиной процессора и другими master-устройствами матричного коммутатора

- Начальная загрузка системы из NOR, NAND FLASH, SPI FLASH, EEPROM или FRAM памяти

- Технология матричного коммутатора (XBS) для одновременного доступа к периферийным модулям или RAM памяти различных ведущих (master) устройств шины

- 64-канальный контроллер прямого доступа к памяти (DMA)

- Контроллер SDRAM, поддерживающий работу 8-битной DDR2 памяти с частотой до 250 МГц

- 32-битный интерфейс внешней памяти FlexBus для поддержки RAM, ROM, MRAM и устройств программируемой логики

- Контроллер USB 2.0 Host (ведущий)

- Контроллер USB 2.0 Host/Device (ведущий/ведомый) с функцией On-The-Go

- Двухканальный контроллер 10/100 Ethernet MAC с функцией контроля/генерации циклического избыточного кода, поддержкой протокола IEEE 1588-2002 и дополнительного Ethernet коммутатора

- Интегрированный в ЦПУ аппаратный ускоритель криптографии с функцией контроля циклическим избыточным кодом и поддержкой алгоритмов DES, 3DES, AES, MD5, SHA-1 и SHA-256

- Генератор случайных чисел

- Расширенный хост-контроллер Secure Digital поддержки карт памяти SD, SDHC, SDIO, MMC и MMCPlus

- Два интерфейса смарт-карт ISO7816

- Два модуля FlexCAN

- Шесть интерфейсов I2C с поддержкой функций DMA в режиме ведущий

- Два синхронных последовательных интерфейса

- Четыре 32-битных таймера с поддержкой функций DMA

- Четыре программируемых таймера прерываний

- 8-канальный 16-битный ШИМ таймер управления двигателем

- Сдвоенный 12-битный АЦП

- Сдвоенный 12-битный ЦАП с поддержкой функций DMA

- Модуль однопроводного интерфейса с поддержкой функций DMA

- Контроллер NAND FLASH памяти

- Часы реального времени с тактовым генератором на 32 кГц, 2 КБайт SRAM и входом питания от батареи

- До четырех последовательных периферийных интерфейсов с поддержкой функций DMA (DSPI)

- До 10 каналов UART с поддержкой однопроводного режима

- До 5 линий IRQ внешних запросов прерывания и 2 пары внешних DMA запросов/извещений

- До 16 высокоскоростных линий ввода/вывода общего назначения (Rapid GPIO) локальной шины процессора

- До 87 стандартных линий ввода/вывода общего назначения

- Рабочий диапазон температур -40…+85°C

- Доступны в корпусах MAPBGA-196 и MAPBGA-256

Область применения

- Автоматизация зданий

- Отладочная плата TWR-MCF5441X-KIT

- Промышленные контроллеры и сети

- Диагностическое оборудование (Не портативное)

- Управление двигателями

- VoIP телефония

|

Datasheet

MCF5441x (1.1 Мб), 11.03.2011 MCF5441x (1.1 Мб), 11.03.2011

Производитель

Где купить

Дистрибуторы

Дилеры

Где купить ещё

|

MCF5441x (1.1 Мб), 11.03.2011

MCF5441x (1.1 Мб), 11.03.2011

MCF5441x Семейство микропроцессоров с архитектурой ColdFire™ (1.1 Мб), 11.03.2011

MCF5441x Семейство микропроцессоров с архитектурой ColdFire™ (1.1 Мб), 11.03.2011