|

Группа компонентов

ARM

Основные параметры

| ЦПУ: Ядро |

ARM926EJ-S

|

| ЦПУ: DSP |

Нет

|

| ЦПУ: FPU |

Нет

|

| ЦПУ: F,МГц |

от 0 до 400

|

| Память: RAM,КБайт |

32

|

| I/O (макс.),шт. |

96

|

| Таймеры: 16-бит,шт |

6

|

| Таймеры: RTC |

Нет

|

| Интерфейсы: UART,шт |

6

|

| Интерфейсы: SPI,шт |

2

|

| Интерфейсы: I2C,шт |

1

|

| Интерфейсы: USB,шт |

2

|

| Интерфейсы: Ethernet,шт |

1

|

| Интерфейсы: DMA,шт |

24

|

| Аналоговые входы: Разрядов АЦП,бит |

10

|

| Аналоговые входы: Каналов АЦП,шт |

4

|

| Аналоговые входы: Быстродействие АЦП,kSPS |

312

|

| VCC,В |

от 1.65 до 3.6

|

| ICC,мА |

350

|

| TA,°C |

от -40 до 85

|

| Корпус |

LFBGA-217

|

Общее описание

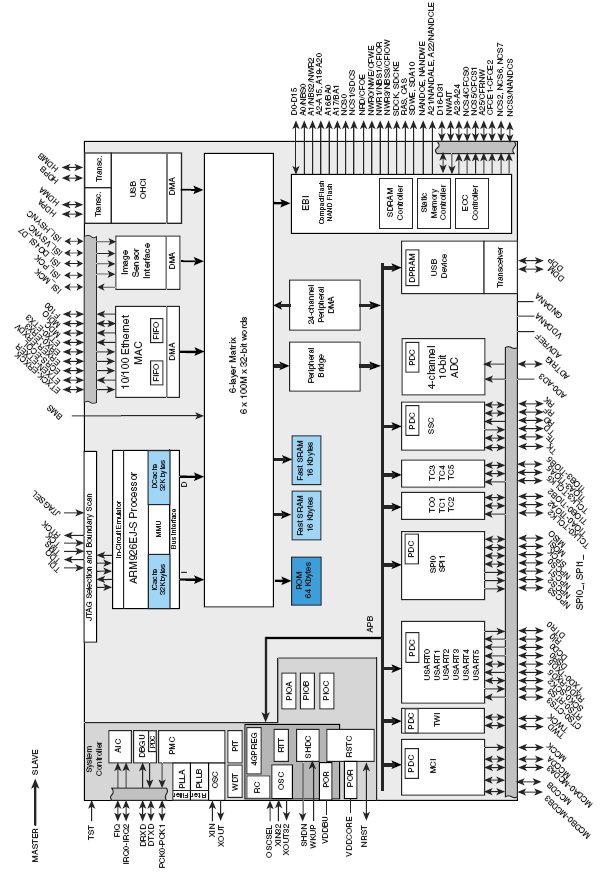

AT91SAM9G20 - микроконтроллер, выполненный путем интеграции процессора ARM926EJ-S с быстродействующими ПЗУ и ОЗУ, а также обширным числом УВВ.

AT91SAM9G20 содержит MAC-контроллер Ethernet, oдин порт USB-устройства и контроллер USB Host. В него также входят ряд стандартных УВВ, в т.ч. УСАПП, SPI, TWI, таймеры-счетчики, контроллер SSC, АЦП и интерфейс MMC-карт.

AT91SAM9G20 использует архитектуру 6-слойной матрицы, что позволяет передавать внутренние потоки данных на большой скорости по шести 32-битным шинам. Кроме того, у него предусмотрен внешний шинный интерфейс (EBI) для подключения к разнообразным внешним запоминающим устройствам.

AT91SAM9G20 является улучшенной версией AT91SAM9260. Они содержат идентичный набор УВВ и совместимы по расположению выводов, за исключением выводов питания. AT91SAM9G20 отличается повышенной до 400 МГц тактовой частотой ARM-ядра и до 133 МГц тактовой частотой системный шины и интерфейса EBI.

Отличительные особенности:

- Выполнен на основе процессора ARM926EJ-S™

- Поддержка DSP-инструкций и технологии ARM Jazelle® для ускорения выполнения Java-инструкций

- 32-кбайт кэш-памяти данных, 32 кбайт кэш-памяти инструкций, буфер записи

- Частота ЦПУ 400 МГц

- Блок управления памятью

- Встроенная отладочная система EmbeddedICE™

- Дополнительные встроенные запоминающие устройства:

- Одно ПЗУ размером 64 кбайт с однотактным доступом на максимальной частоте

- Два статических ОЗУ размером 16 кбайт с однотактным доступом на максимальной частоте

- Внешний шинный интерфейс (EBI)

- Поддержка синхронных динамических ОЗУ, статической памяти, NAND Flash памяти с функцией ECC и Flash памяти CompactFlash®

- Полноскоростной (12Мбит/сек) Device порт USB 2.0

- Встроенные трансивер и 2432 байт двупортового ОЗУ

- Полноскоростной (12Мбит/сек) Host и Double-порт USB 2.0

- один или два встроенных трансивера

- встроенные буферы FIFO и выделенные каналы ПДП

- MAC-контроллер Ethernet 10/100 Base T

- Интерфейс MII или RMII

- 128-байтные буферы FIFO и выделенные каналы ПДП для приема и передачи данных

- Интерфейс фотоприемника изображения

- Интерфейс ITU-R BT. 601/656 с программируемой частотой захвата изображения

- 12-битный интерфейс передачи данных для поддержки высокочувствительных фотоприемников изображения

- Синхронизация SAV и EAV, канал предварительного просмотра с возможностями масштабирования, формат YCbCr

- Матрица шин

- Матрица из шести 32-битных слоев

- Возможность выбора режима загрузки, поддержка команды Remap

- Полнофункциональный контроллер сброса, в т.ч.:

- Контроллер сброса, контроллер отключения

- Четыре 32-битных регистра (16 байт) с резервируемым питанием

- Тактовый генератор и контроллер управления энергопотреблением

- Улучшенный контроллер прерываний и блок отладки

- Интервальный таймер, сторожевой таймер и часы реального времени

- Контроллер сброса (RSTC)

- Выполнен на основе схемы сброса при подаче питания; идентификация источника сброса и управление выходом сброса

- Тактовый генератор (CKGR)

- Низкочастотная синхронизация: опциональный маломощный генератор частоты 32768 Гц или внутренний маломощный RC-генератор с резервируемым питанием

- Высокочастотная синхронизация: встроенный генератор частоты 3…20МГц и две схемы ФАПЧ для синтеза частот до 800 МГц и до 100 МГц.

- Контроллер управления энергопотреблением (PMC)

- Режим работы с синхронизацией очень низкой частотой, возможности программной оптимизации энергопотребления

- Два программируемых внешних сигнала синхронизации

- Контроллер прерываний (AIC)

- Индивидуальное маскирование, 8 уровней приоритета, векторизованные источники прерываний

- Три внешних источника прерываний и один быстродействующий источник прерывания, защита от ложной генерации прерываний

- Блок отладки (DBGU)

- 2-проводной интерфейс УАПП и поддержка отладочного коммуникационного канала, возможность программируемого ограничения доступа со стороны встроенной отладочной системы

- PIT-таймер

- 20-битный интервальный таймер и 12-битный счетчик интервалов

- Сторожевой таймер (WDT)

- Защищен ключом, однократное программирование, оконный 16-битный счетчик с низкочастотной синхронизацией

- Таймер реального времени

- 32-битный циклический счетчик с низкочастотной синхронизацией и 16-битным предделителем

- Один 4-канальный 10-битный АЦП

- Три 32-битных контроллера параллельного ввода-вывода (PIOA, PIOB, PIOC)

- 96 программируемых линий ввода-вывода, каждая из которых мультиплексирована с одним или двумя встроенными УВВ

- Возможность генерации прерывания по изменению состояния любого из входов

- Индивидуальные настройки каждой линии: выход с открытым стоком, подтягивающий резистор и синхронизированный выход

- На всех линиях ввода-вывода в канале ввода предусмотрены триггеры Шмита

- Контроллер ПДП встроенных УВВ (PDC)

- Один интерфейс карт Flash памяти MMC

- Совместимость с картами SDCard/SDI

- и MultiMediaCard™

- Автоматическое управление протоколом и быстродействующая автоматическая передача данных с использованием PDC

- Один контроллер синхронной последовательной связи SSC

- Раздельные сигналы синхронизации в каналах приема и передачи

- Поддержка протокола I2S и мультиплексирования с разделением по времени

- Возможности высокоскоростной передачи 32-битного потока данных

- Четыре универсальных синхронных/асинхронных приемо-передатчика (УСАПП)

- Раздельные генераторы скорости связи, поддержка IrDA® модуляции/демодуляции и Манчестер кодирования/декодирования

- Поддержка смарт-карт ISO7816 T0/T1, аппаратного подтверждения связи и протокола RS485

- Полный интерфейс управления модемом у УСАПП0

- Два 2-проводных УАПП

- Два ведущих/подчиненных последовательный интерфейса SPI

- Программируемая длина данных от 8 до 16 бит, четыре выхода выбора внешних ИС

- Синхронная передача данных

- Два трехканальных 16-битных таймера/счетчика

- Три входа внешней синхронизации, две линии ввода-вывода общего назначения в каждом канале

- Два канала ШИМ, режим захвата/генерации импульсов, возможность двунаправленного счета

- Выходы TIOA0, TIOA1, TIOA2 с повышенной нагрузочной способностью

- Один двухпроводной интерфейс TWI

- Совместимость с ИС запоминающих устройств, оснащенных стандартным 2-проводным последовательным интерфейсом

- Одно-, двух- или трехбайтный подчиненный адрес

- Возможность чтения/записи последовательности байт

- Работа в режимах мастер, мультимастер и подчиненный

- Скорость передачи до 400 кбит/сек

- Поддержка общего вызова в подчиненном режиме

- Возможность работы совместно с PDC для высокоскоростной передачи данных в режиме мастер

- Граничное сканирование по стандарту IEEE® 1149.1 JTAG на всех цифровых выводах

- Напряжения питания

- VDDBU, VDDCORE, VDDPLL = 0.9…1.1В

- VDDOSC = 1.65…3.6 В

- VDDIOP (УВВ) = 1.65…3.6В

- VDDUSB = 3.0…3.6В

- VDDANA (АЦП) = 3.0…3.6В

- VDDIOM (ввод-вывод запоминающих устройств) = 1.65…1.95В или 3.0…3.6В

- Доступность в 217-выводном RoHS-совместимом корпусе LFBGA

|

Datasheet

AT91SAM9G20 (11.9 Мб), 25.11.2008 AT91SAM9G20 (11.9 Мб), 25.11.2008

Производитель

Где купить

Дистрибуторы

Дилеры

Где купить ещё

|

AT91SAM9G20 (11.9 Мб), 25.11.2008

AT91SAM9G20 (11.9 Мб), 25.11.2008

AT91SAM9G20 Микроконтроллер AT91 ARM Thumb (11.9 Мб), 25.11.2008

AT91SAM9G20 Микроконтроллер AT91 ARM Thumb (11.9 Мб), 25.11.2008

AT91SAM9G20 Микроконтроллер AT91 ARM Thumb. Краткая информация (1.1 Мб), 25.11.2008

AT91SAM9G20 Микроконтроллер AT91 ARM Thumb. Краткая информация (1.1 Мб), 25.11.2008

ARM926EJ-S Справочное руководство по процессору ARM926EJ-S (1.6 Мб), 05.06.2008

ARM926EJ-S Справочное руководство по процессору ARM926EJ-S (1.6 Мб), 05.06.2008

ARM9E-S Справочное руководство по процессору ARM9E-S (4.1 Мб), 05.06.2008

ARM9E-S Справочное руководство по процессору ARM9E-S (4.1 Мб), 05.06.2008

Архитектура и система команд RISС-процессоров семейства ARM (Рус)

Архитектура и система команд RISС-процессоров семейства ARM (Рус)